We're seeing a failure to boot Linux on ARM core 0 of a K2K/K2H device.

When a the processor is placed in no-boot mode, brought out of reset and u-boot is loaded via code composer, the boot process hangs before Linux is booted. Building u-boot with 'DEBUG' defined and adding additional printf statements revealed that the function mon_install() is called but doesn't ever return. This function installs the boot monitor contained in the file 'skern.bin'. If the processor is paused at this stage and u-boot is reloaded the boot will then succeed. If the processor is power cycled and u-boot is reloaded the boot will fail again at the same point. So, cold boot fails and warm boot succeeds. This appears to be fairly consistent.

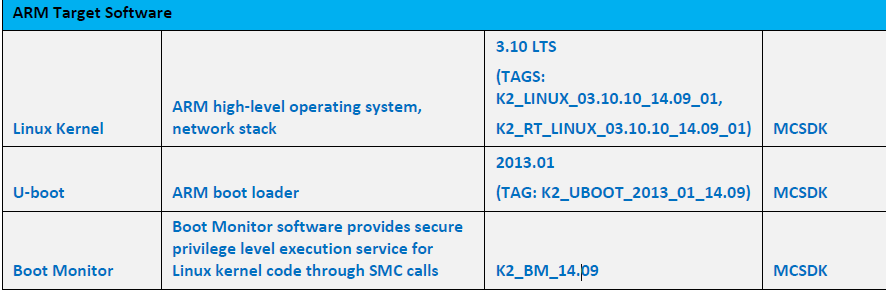

This problem occurs only with 'skern.bin' built using bitbake. 'skern.bin' provided by TI as part of MCSDK 3.00.03.15 works correctly. The SRCREV used by the boot-monitor bitbake recipe in MCSDK is 4b0287a3fa9c7a25c75bbe3a54f4ac2a92dc0aaa which is the latest git commit to this repo. This recipe was modified to use an older git commit and it was found that it is possible to build a working 'skern.bin' from git commit 51371402f979645478f2bc2be170279acee87be6 or earlier. Commit 6013a66b3ba1376a3de51c32d077c642fb0bf791 or later exhibits the failure. This suggests that commit 6013a66b3ba1376a3de51c32d077c642fb0bf791 introduced the error.

If the processor is placed in EMIF boot mode this failure is not seen - the latest version of 'skern.bin' consistently allows a successful boot. The issue is only seen when the processor is in no-boot mode and u-boot is loaded via Code Composer.

The commit which is suspected of introducing the error is shown below:

commit 6013a66b3ba1376a3de51c32d077c642fb0bf791

Author: Vitaly Andrianov <vitalya@ti.com>

Date: Mon Jun 9 09:51:12 2014 -0400

boot-monitor: set NSACR.NS_SMP bit

SMP Linux kernel sets the ACTRL.SMP bit. We need to set NSACR.NS_SMP bit

to make the ACTRL.SMP writable form non-secure world.

Signed-off-by: Vitaly Andrianov <vitalya@ti.com>

diff --git a/sec/skern.c b/sec/skern.c

index 58550bb..ec68847 100644

--- a/sec/skern.c

+++ b/sec/skern.c

@@ -248,6 +248,10 @@ void skern_setup_cp15(void)

"mcr p15, 0, r0, c1, c0, 1\n"

"isb\n"

"dsb\n"

+ /* set NSACR.NS_SMP bit */

+ "mrc p15, 0, r0, c1, c1, 2\n"

+ "orr r0, r0, #(1 << 18)\n"

+ "mcr p15, 0, r0, c1, c1, 2\n"

"mov r0, #0x00f00000\n"

"mcr p15, 0, r0, c1, c0, 2\n"

"isb\n"

This sequence of instructions has been mentioned as the cause of a processor hang in another post on E2E: e2e.ti.com/.../1321339.

Is the above instruction sequence known to cause a hang on K2K/K2H processors? Has the latest boot-monitor code been tested on these devices? And is there anything we can do to workaround or fix this issue?

Thanks,

Paul Barker