In pdk_C6657_1_1_2_6\packages\ti\csl\cslr_bootcfg.h, the register locations define is based on the struct "CSL_BootcfgRegs", but some register offsets are not same as the offsets indication in Device State Control Registers in latest C665x datasheet.

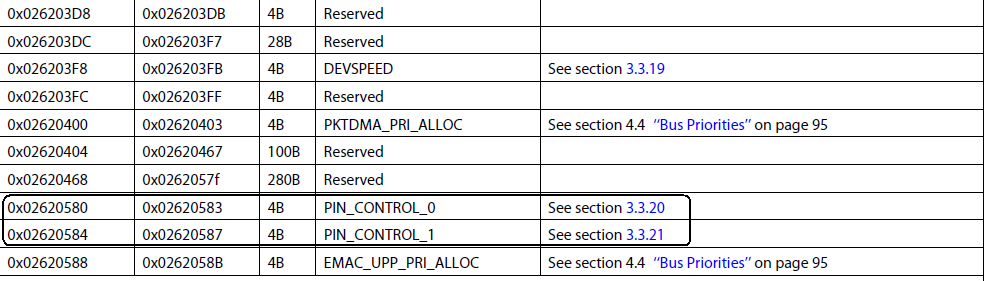

For example,CHIP_PIN_CONTROL_0 are located as below in CSL_BootcfgRegs, but the offset indication in datasheet is captured as below picture.

Which one should be followed?

volatile Uint32 MARGIN1;

volatile Uint32 MARGIN2; // new

volatile Uint32 MARGIN3;

volatile Uint32 MARGIN4;

volatile Uint32 MARGIN5;

volatile Uint32 CHIP_PIN_CONTROL_0;

volatile Uint32 CHIP_PIN_CONTROL_1;

volatile Uint32 REGS_UID0;

volatile Uint32 REGS_UID1;

volatile Uint32 REGS_UID2;

volatile Uint32 REGS_UID3;

volatile Uint32 REGS_CUST_EFUSE_RSVD_0;

volatile Uint32 REGS_CUST_EFUSE_RSVD_1;

volatile Uint32 REGS_CUST_EFUSE_RSVD_2;

volatile Uint32 REGS_CUST_EFUSE_RSVD_3;

volatile Uint32 REGS_CONTROL_SEC_EMU;