Hello,

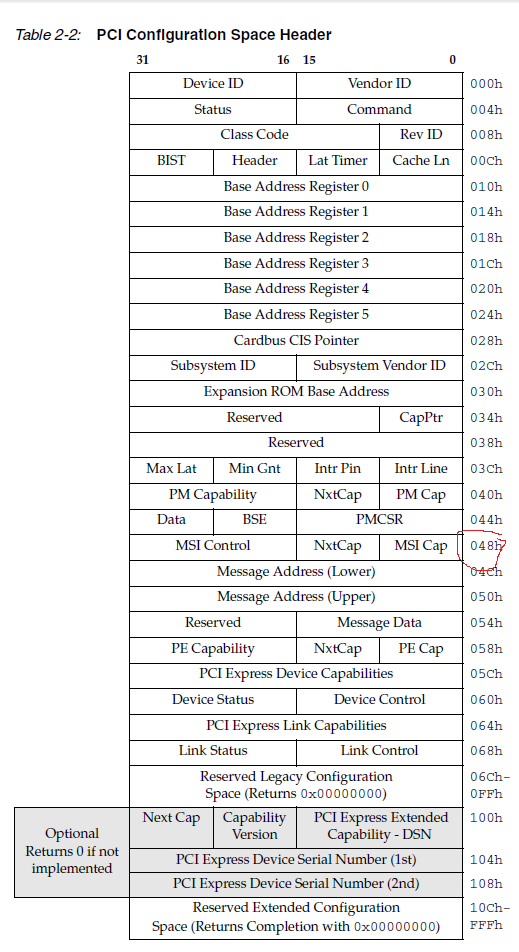

I am working to connect C6670 to Spartan6 FPGA over PCIe. One trouble I see was behaviour of configuration space accesses. I have just realized, that configuration space layout is coded differently in DSP and FPGA. As per FPGA, Xilinx UG654 defines PCI configuration header as follows:

Please note, that at 0x34 there is s capability pointer, which points to PM Cap at 0x40, which in turn points to 0x48, where MSI Cap is located. The numbers in NxtCap pointers do agree with expected when I dump complete config space of FPGA.

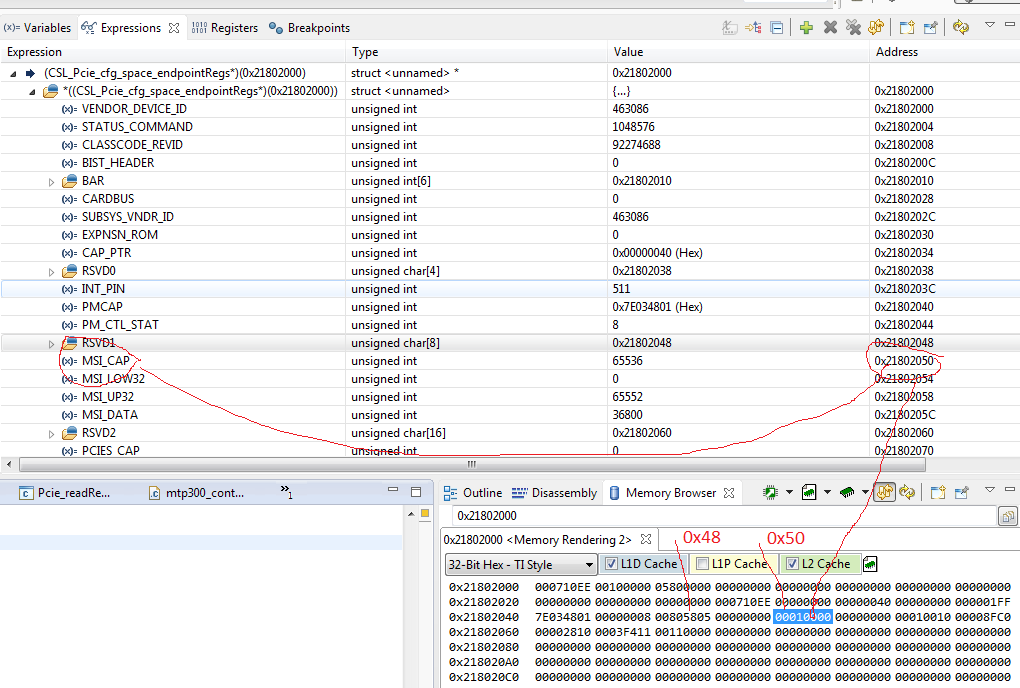

When playing with MSI capability from DSP side, I have noticed, that msiEn bit was written to wrong location. While I expected it to go to config register at 0x48, the bit appeared in register at 0x50. There is no surprise, that FPGA does not operate properly with such a setting. Then I traced PCIe endpoint config space layout in pdk_C6670_1_1_2_6\packages\ti\csl\cslr_pcie_cfg_space_endpoint.h. Particularly, please see the following:

typedef struct {

volatile Uint32 VENDOR_DEVICE_ID;

volatile Uint32 STATUS_COMMAND;

volatile Uint32 CLASSCODE_REVID;

volatile Uint32 BIST_HEADER;

volatile Uint32 BAR[6];

volatile Uint32 CARDBUS;

volatile Uint32 SUBSYS_VNDR_ID;

volatile Uint32 EXPNSN_ROM;

volatile Uint32 CAP_PTR;

volatile Uint8 RSVD0[4];

volatile Uint32 INT_PIN;

volatile Uint32 PMCAP;

volatile Uint32 PM_CTL_STAT;

volatile Uint8 RSVD1[8];

volatile Uint32 MSI_CAP;

...

} CSL_Pcie_cfg_space_endpointRegs;

Please notice there are 8 bytes (=2 DWORDS) of RSVD1 between PM_CTL_STAT and MSI_CAP fields. There is no such a reserved space in Xilinx FPGA. Because of that FPGA expects MSI capabilities to exist at 0x48, but DSP writes them to 0x50. One can see that in the following sreenshot

I have just executed the line

setRegs.msiCap = &MsiCap; MsiCap.msiEn = 1; if ( pcie_RET_OK != Pcie_writeRegs(handle, pcie_LOCATION_REMOTE, &setRegs) )...

I expected value of 0x00010000 to be written over 0x48, but in fact that value was written to 0x50.

So the definition of endpoint address space in CSL does not match layout of actual config space in FPGA.

I'm afraid, I cannot use relevant part of PCIe LLD because of the above mentioned discrepancy, so have to write my own code to handle FPGA, but just wonder, what is rationale of having config space defined with reserved gaps, as in CSL?