I have a problem setting up the GPMC for synchronous access on a AAD device (an FPGA).

Asynchronous access works fine with these register settings:

WR_MEM_32(GPMC_CONFIG1(FPGA_GPMC_CS), 0x00001100);

WR_MEM_32(GPMC_CONFIG2(FPGA_GPMC_CS), 0x00060A00);

WR_MEM_32(GPMC_CONFIG3(FPGA_GPMC_CS), 0x11030302);

WR_MEM_32(GPMC_CONFIG4(FPGA_GPMC_CS), 0x05044804);

WR_MEM_32(GPMC_CONFIG5(FPGA_GPMC_CS), 0x0008060A);

WR_MEM_32(GPMC_CONFIG6(FPGA_GPMC_CS), 0x06040000);

WR_MEM_32(GPMC_CONFIG7(FPGA_GPMC_CS), 0x00000010);

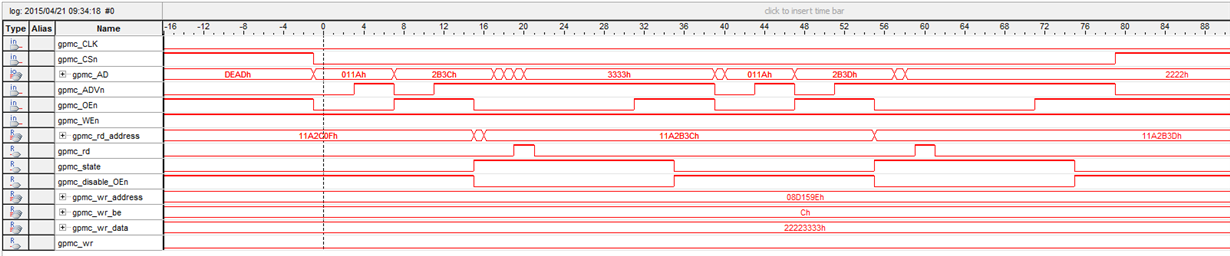

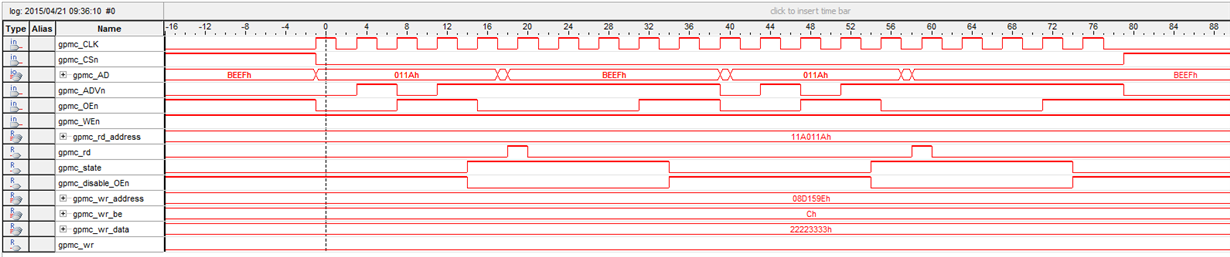

But as soon as I change the read and write type bits to 1 (synchronous access), I can see the clock being enabled during access, but the address/data lines always stay at 0x0000 (data during write access is set properly, and also data is read - though both will obviously only work on address 0).

WR_MEM_32(GPMC_CONFIG1(FPGA_GPMC_CS), 0x28001100);

WR_MEM_32(GPMC_CONFIG2(FPGA_GPMC_CS), 0x00060A00);

WR_MEM_32(GPMC_CONFIG3(FPGA_GPMC_CS), 0x11030302);

WR_MEM_32(GPMC_CONFIG4(FPGA_GPMC_CS), 0x05044804);

WR_MEM_32(GPMC_CONFIG5(FPGA_GPMC_CS), 0x0008060A);

WR_MEM_32(GPMC_CONFIG6(FPGA_GPMC_CS), 0x06040000);

WR_MEM_32(GPMC_CONFIG7(FPGA_GPMC_CS), 0x00000010);

Am I doing something wrong / missing some crucial things?

Thank You in advance for any helpful answers.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.