Hello,

Problem with McBSP and EDMA3.

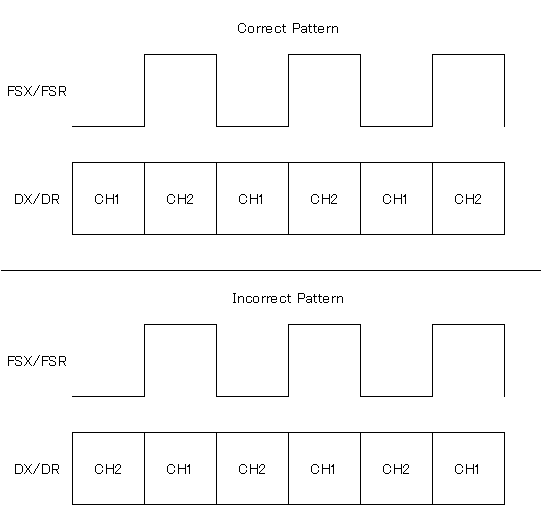

Channel reversal is occurred about once in five times.

Data corresponding to FSX/FSR is reversed as seen in the pictures below.

Transfer format is I2S(32bit, 2ch).

EDMA3 is used to transfer data between McBSP and buffer.

I initialize McBSP according to Technical Reference Manual.

("TMS320C6748 DSP Technical Reference Manual 24.2.12 McBSP Initialization Procedure")

I need to switch sampling rate(44.1kHz, 48kHz, 88.2kHz, etc.).

McBSP is stopped before each switching.

Sampling rate switching is processed as shown below.

Channel reversal is occurred after starting McBSP.

* stop McBSP and EDMA3

* switch frequency of CLKS

* start McBSP and EDMA3 according Technical Reference Manual.

Once McBSP and EDMA are started correctly, channel reversal is not occurred until the modules are stopped.

This problem appears in both TX and RX.

FIFO is not related with this problem.

I tried the method written in "TMS320C6748 DSP Technical Reference Manual 24.2.12.2 Special Case: External Device is the Transmit Frame Master" and "processors.wiki.ti.com/index.php", but the problem is not resolved.

I would like to resolve this problem.

Thanks.