We are the AM3358 processor in our Gateway design (designed around BeagleBone Black core). We were using the Angstrom Linux interface to trigger the on-board processor watchdog, but we had board hang in the field. We suspect that Linux stopped running our program and thus also turned off the on-board watchdog. We have tested the watchdog by putting our program into an infinite loop and our board rebooted. Therefore, something happened to our program and the board had to be power cycled. I know what was causing our program to die, but I have lost confidence in the processors watchdog/Linux interface to watchdog.

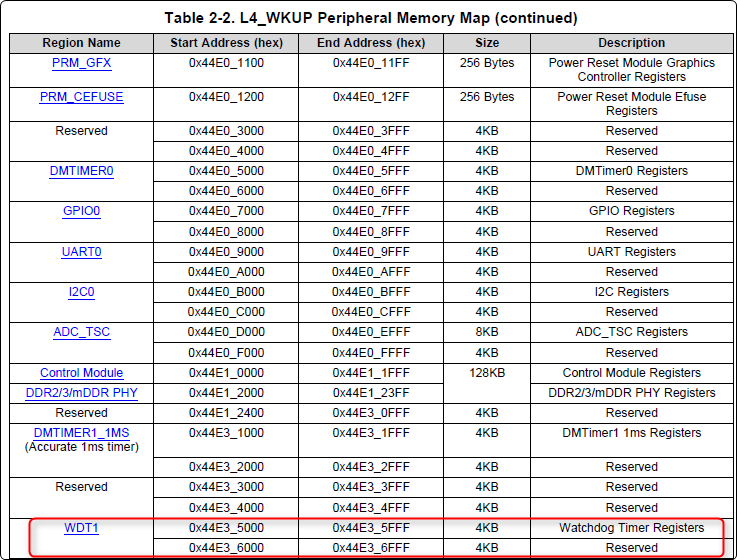

I thought fine I will just write the code myself to control the watchdog directly. So I looked up in the watchdog in the Technical Reference to get the address of the register address and it said the Physical Address is “L4 Wakeup slave port”. I cannot find any real description of the port or a physical address and register specifics. I looked for sample code – struck out with that.

Bottom line I need technical help on controlling the on-board watchdog on the AM3358 processor from our code.