We have an ST Micro LIS3DH "nano" Accelerometer connected via i2c-2 to a Rev. c (Debian) Circuitco Beaglebone Black.

The LIS3DH has a hard-coded base address of 0x30.

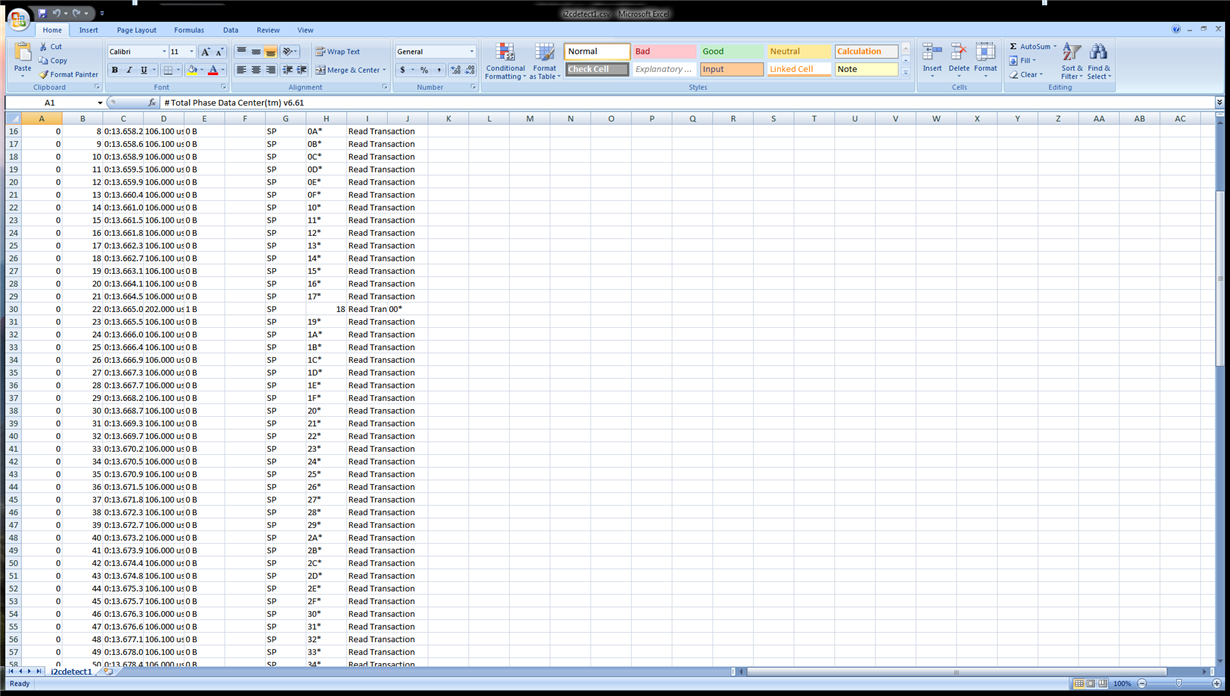

However, when I run "i2cdetect -r 2" it finds a device at 0x18 *not* 0x30. Since 0x18 = 11000 in binary and 0x30 = 110000 in binary, it would appear that the LIS3DH is seeing the traffic on the i2c bus bit-shifted 1 bit to the left, so that it "thinks" it saw a 0x30 when the driver placed a 0x18 on the bus.

Indeed, when using test code, ported from an application written for another processor which successfully tasked the LIS3DH and did not exhibit framing errors, I do not get a response when I try to address 0x30. However, I do get a reaction from the LIS3DH when I target bass address 0x18. From there it gets muddled, since reads and writes appear to have bit framing errors as well and since a read is indicated in i2c protocol by *setting* the LSB and since the LSB is getting shifted up, I can't really find a way to successfully read the device.

I note that the maximum clock rate for i2c is 100 kHz, and that's what the bus is set to (and I have yet to find a way to change it).

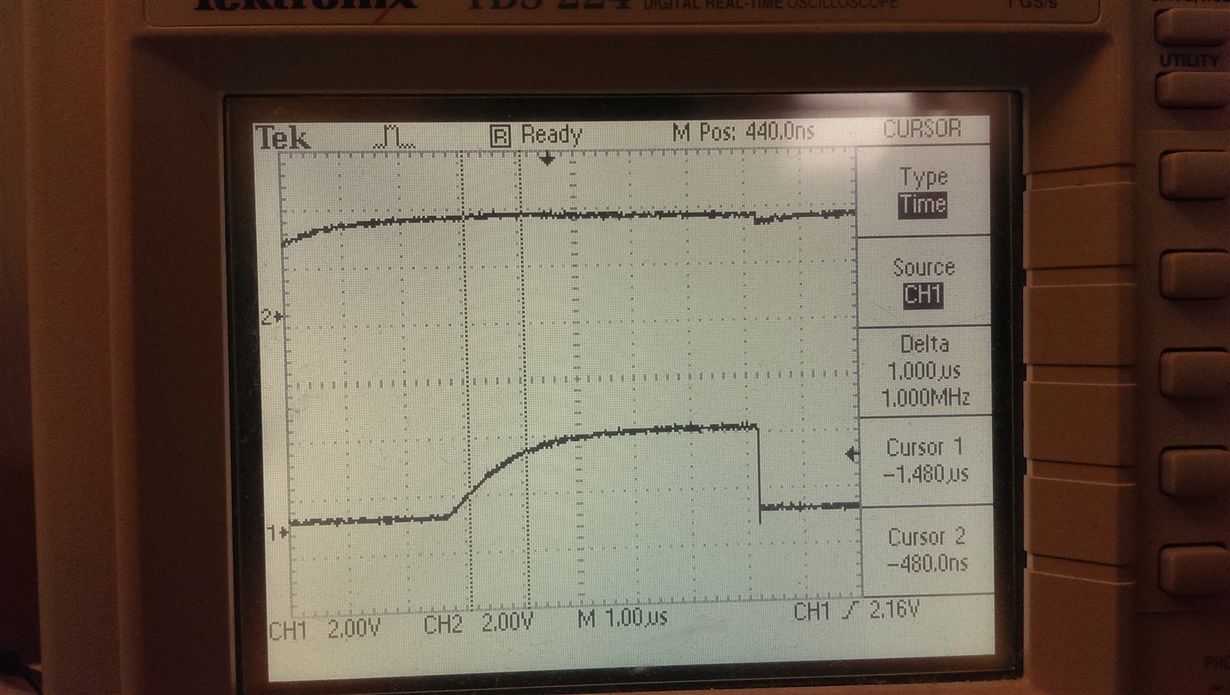

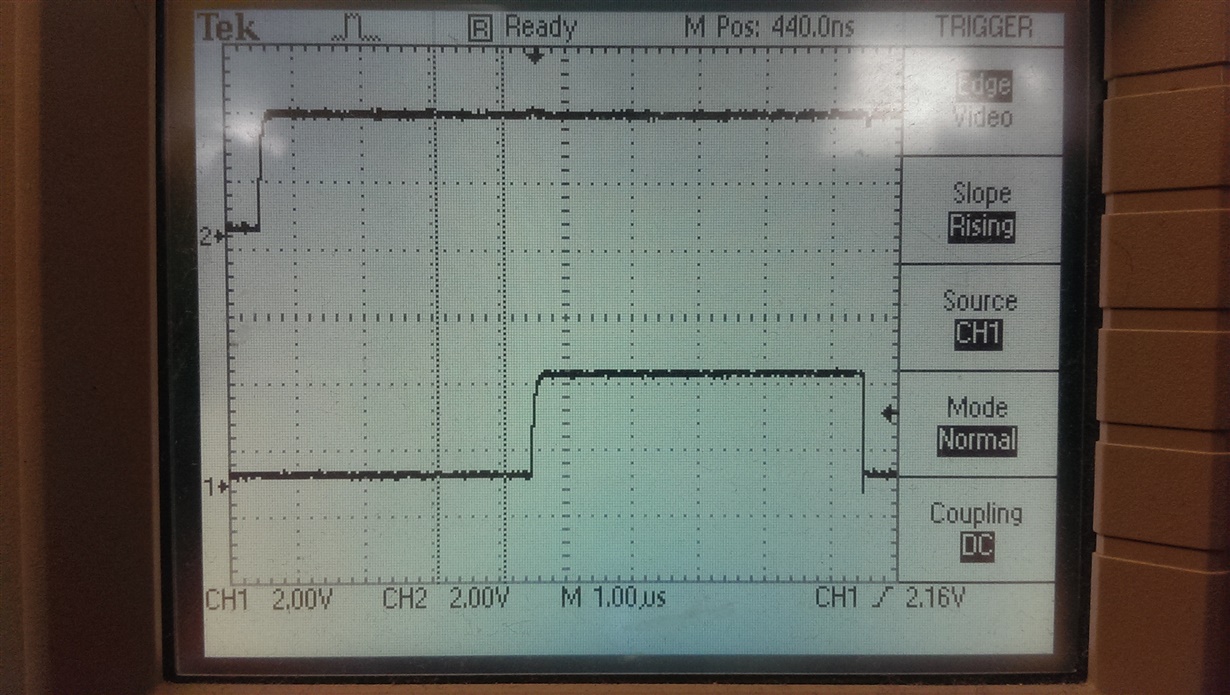

Also, the maximum rise time for SCL is 1000 ns. Look at the scope trace below, the bottom trace is SCL (the top trace is SDA). Also note that I have placed the cursors at a spacing to indicate exactly 1000 ns. It would appear that the rise time (from 0.2*Vcc to 0.8*Vcc) is right at the cusp of being 1000 ns, perhaps even slightly longer.

Could the 1000 ns rise time, combined with the absolute maximum clock rate (100 kHz), be causing the bit framing error?

Can the clock rate of the i2c bus be adjusted?

It would appear that if I disconnect the LIS3DH, the rise time of the SCL line wagging into the open air goes down to about 700 ns, so there may be room to get some capacitance out of the lines going to the LIS3DH and improve this a bit.

Thanks for any help you can give.

Mark Sutton

Globalstar, INC.