Revision H of "Powering the AM335x with the TPS65217x" moved VDDS from LDO3 to LDO1 when using DDR3(L), and this change was also implemented in BeagleBone Black (rev A6A) with the comment:

This change was based on an alert we just received from TI that there is a power sequencing issue with the TPS65217C power management IC and the power sequencing is incorrect. This change connects the VDDS rail to the VRTC rail. We do not believe at this time, that the issue is causing any issues with the boards, but we want to comply with the directive.

I've been investigating power management on the BBB in detail (mostly in relation to its 3v3b-regulator bug), and along the way noticed that during shutdown the 3v3 rail (LDO4) leveled off at around 1.3V until LDO1 shuts off at strobe 15, after which it would finally start to drop to zero.

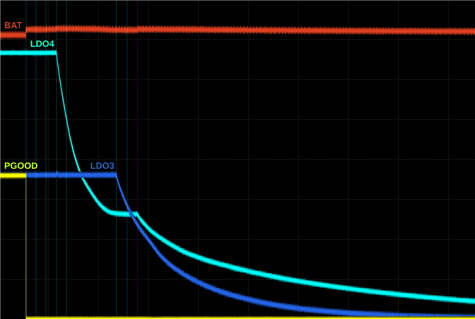

This shows various PMIC terminals on a BBB (patched to fix the 3v3b-issue) during an ACTIVE-to-OFF transition (while powered through BAT using a variable PSU at 3.6V):

Note the supply rail dip once the 1.8V rails begin to leak to the 3.3V rail, and the sudden jump upward at strobe 15 indicating significant current was flowing through LDO1 at the time it was shut off. In fact, if a transition into SLEEP-state is done, the 3.3V rail remains at 1.3V indefinitely and the BAT current measured in this state was quite significant (iirc ~ 45 mA).

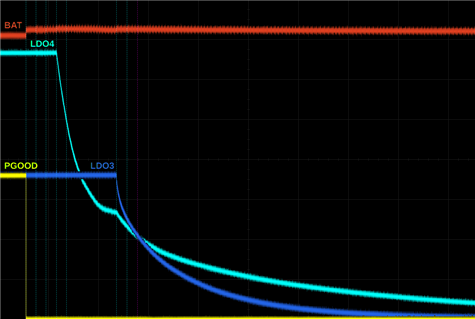

As experiment, VDDS was reconnected to LDO3 instead of LDO1 (by moving resistor R8 to R9). I did not notice any difference during powerup, but shutdown changed significantly:

Leakage evidently still occurs, but the duration of this situation appears substantially reduced. Transition to SLEEP-state (RTC-only sleep) in this case works normally, and produces essentially the same plot as the transition to OFF-state depicted above (since LDO1 wasn't included in these measurements).

So this leaves me with a few questions:

What exactly was the motivation to move VDDS from LDO3 to LDO1? It seems to me that any undesirable current flow resulting from the late startup or early shutdown of VDDS would have to be occurring between strobes 1 and 2, from VDDS_DDR to VDDS, but I see no evidence of such flow: the current consumption pattern (as estimated by power supply fluctuations) during powerup appears unaffected by moving VDDS, and strobe 1 has no visible effect on the LDO3 voltage during powerup or shutdown. However, since I do not have measurements of all rails nor accurate current measurements I may be overlooking something.

Why does the VDDS-to-VDDHV leakage only seem to occur on shutdown, and not on powerup? Unlike the other supply rails it is not really clear at all what the purpose of VDDS is, and I have trouble constructing a mental model of what is going on here.

Given such asymmetry between powerup and shutdown, might it make sense to alter the PMIC sequencer settings prior to initiating shutdown?