Hi all.

I'm using an AM3359 with code composer (6.1.0.00104 ) and sysbios (6.40.3.39).

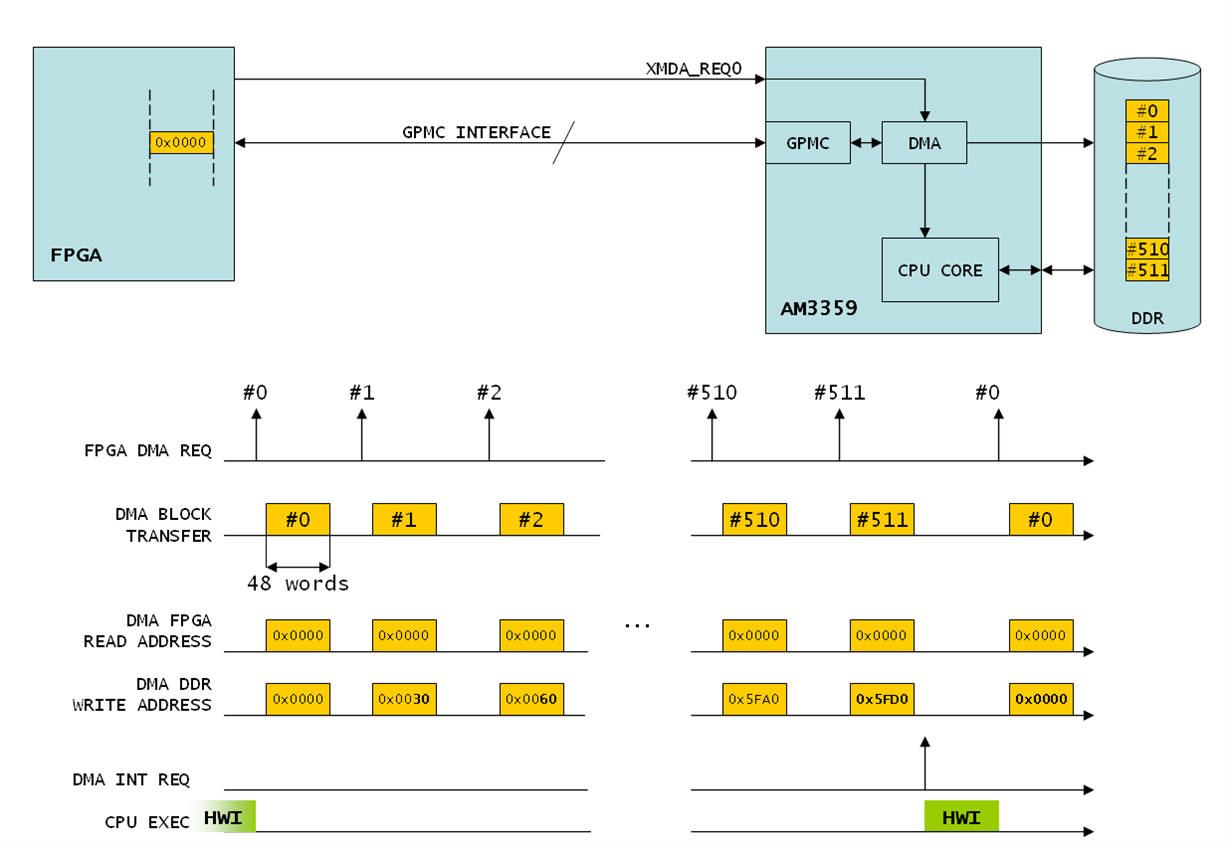

I need to transfer from an external FPGA ( connected through GPMC controller ) 512 blocks of data; the length of each block is 48 words. Each block transfer is triggered by an FPGA signal.

At the end of the entire sequence of 512 transfers, the CPU needs to receive an interrupt to perform its task on newly transferred data. After that, the entire sequence has to restart and so on.

FPGA sources the 48 words block always at the same starting address (ex: 0x0000); this block must be copied at successive DDR addresses:

- first DMA cycle reads from FPGA at 0x0000 and writes to DDR at 0x0000

- second DMA cycle reads from FPGA at 0x0000 and writes to DDR at 0x0030

- third DMA cycle reads from FPGA at 0x0000 and writes to DDR at 0x0060

- ...

- last DMA cycle reads from FPGA at 0x0000 and writes to DDR at 0x5FD0

I was wondering about "linking transfers", but the PaRAM memory has only 256 elements: I need *at least* 512 transfers.

I can't awake the CPU at every single block transfer to reprogram the PaRAM data, because of excessive CPU load.

Suggestions?