Other Parts Discussed in Thread: TVP5146

Hi,

what ISIF and IPIPEIF register do I have to set when using a camera in 8bit BT656 mode?

I know the REC656IF register in ISIF, and also the 8bit per pixel pack mode etc. But I am not sure about HD/VD/FLD polarities in both ISIF and IPIPEIF. I also can't find out if I should set the internal HD/VD timing generator register in ISIF (PPLN, LPFR and MODSET.HDVDD).

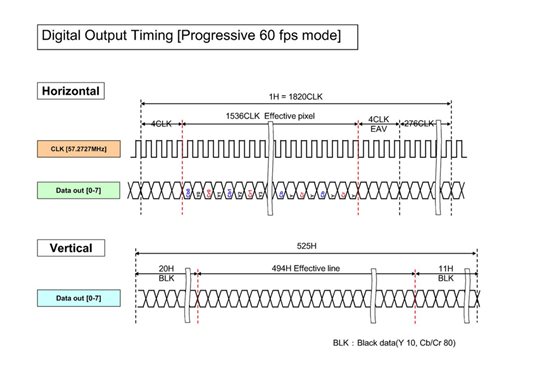

I am also attaching the BT656 timing of my camera to this post.

I would appreciate some more information regarding BT656 input and/or an example register setting.

Thank you.

Sebastian