Hello everyone,

Target is C6678.

I have a question about the PCIe architecture for this device.

I didn't find answers about it in the User Guide, nor the wiki nor the forum

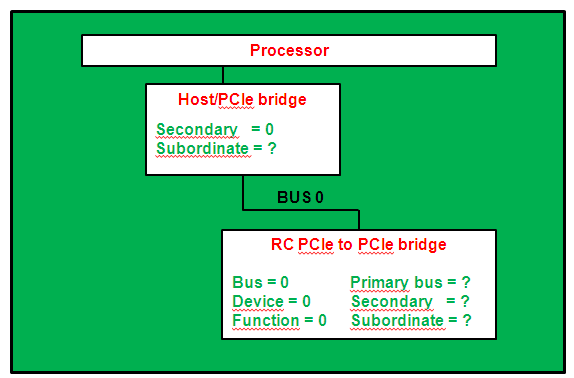

To me the C66x Root Complex architecture (inside "PCIe core") is like this

It's the user responsability (or operating system enumeration software) to generate

a Type 0 configuration request targeting BDF 0/0/0 to setup the Primary/secondary/subordinate bus values and other things.

Tell me if I'm wrong.

Also sometimes in the PCIe classic litterature (for example PCI Express Technology book) the Root Complex is shown like this

Can you confirm to me that in the C66x root complex architecture

there is no secondary and subordinate bus to set up in the Host/PCIe bridge ?

Thank you

Regards,

Clement