Other Parts Discussed in Thread: OMAPL138

I wish to use the uPP in receive mode, and am trying to combine the bits and pieces of information from the data sheet (SPRS590F), tech ref (spruh79a), and uPP User's guide(sprugj5b).

Tech Ref, section 6.3.5, on uPP Clocking, tells us that "The uPP subsystem requires a module clock to drive its internal logic" etc. Also, "The module clock is always sourced by PLL0_SYSCLK2". The uPP User’s guide adds the detail that the module clock must be no more than ½ the CPU clock speed.

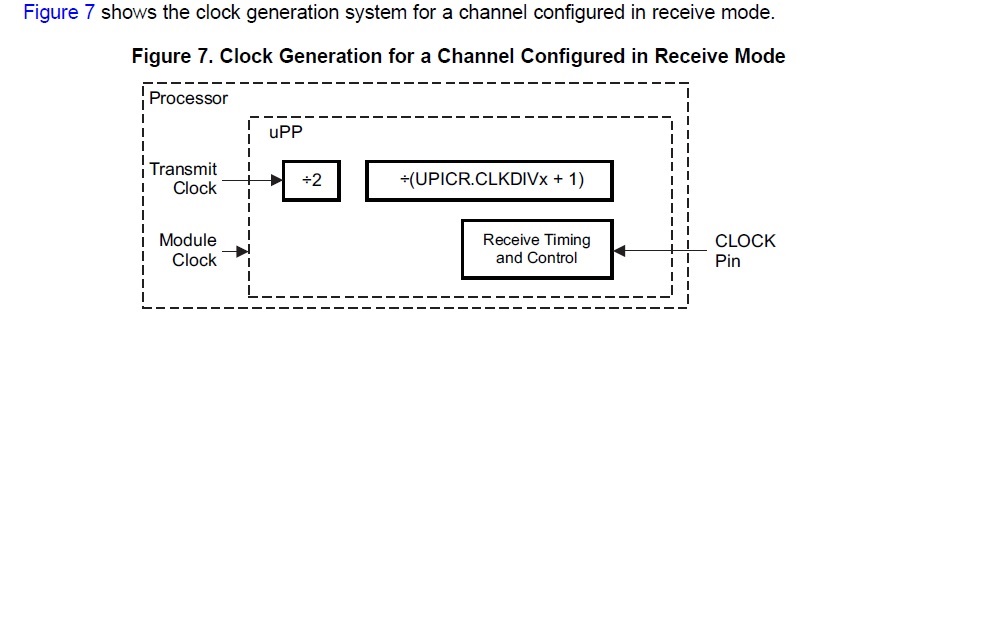

In the diagrams in the uPP User's guide and in the tech ref, we see a block like this

which shows us the same module clock, along with an input receive clock, and also a transmit clock. It mentions that the input on CLOCK pin must be at maximum ¼ of the CPU clock speed.

which shows us the same module clock, along with an input receive clock, and also a transmit clock. It mentions that the input on CLOCK pin must be at maximum ¼ of the CPU clock speed.

The data sheet sprs590F has detailed timing for the signal on the clock pin relative to the data, but makes no mention of the Module clock.

So … after piecing together the details from these three documents, I am still lacking two bits of information.

1) Is there any requirements on the module clock relative to the receive clock? Perhaps it must be twice as fast?

2) In receive mode, do I need a transmit clock? From the text, I would think that I do not, but from Figure 7, it seems to hint that I do need it. If I need it, what is the requirement relative to the module clock and the receive clock on the CLOCK pin?

Thanks