Other Parts Discussed in Thread: TPS65910

Hi,

I have some question about AM335x power down sequence.

Could you please answer my question?

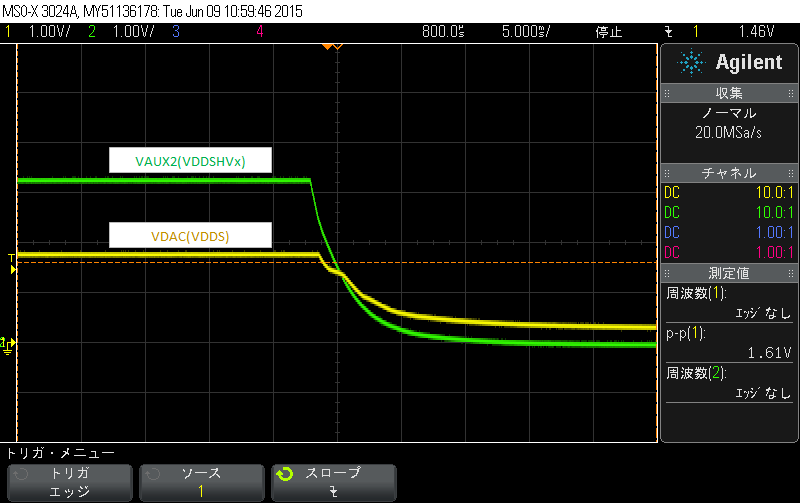

I have gotten the waveform of VDAC(VDDS) and VAUX2(VDDSHVx) on AM335xEVM.

I suspect that it violates the following description on AM335x datasheet.

"It is recommended to maintain VDDS ≥1.5V as all the other supplies fully ramp down to minimize in-rush currents."

Does this waveform violates this description?

If yes, please tell me what I should do to solve this.

Best regards,

Keigo Ishii