Hello.

I'm successful in sending and receiving data through MCASP0 with interrupt. I'm using QuickStartOMAPL1x rCSL mcasp example, slaved for my board.

I'm change my example for receiving data through EDMA 3. (using parts of code from this example software-dl.ti.com/.../index_FDS.html). But I don't go to the interrupt handler function. EDMA3CC_INT1_isr isn't triggering.

I am followed by sequence from SPRUFM1 document (2.4.1.2 Transmit/Receive Section Initialization), but it does not solve the problem.

This is my code:

#include <stdio.h>

#include <c6x.h>

#include <cslr_gpio.h>

#include <cslr_mcasp.h>

#include <cslr_syscfg_C6745.h>

#include <soc_C6745.h>

#include <cslr_psc_C6745.h>

#include <cslr_dspintc.h>

#include <cslr_edma3cc.h>

#define SAMPLES_PER_BUF 128

#define BYTES_PER_SAMPLE 4

#define N_CHANNELS 2

#define BUF_LENGTH SAMPLES_PER_BUF * N_CHANNELS

#define BUF_SIZE SAMPLES_PER_BUF * N_CHANNELS * BYTES_PER_SAMPLE

#define MCASP0_BASE 0x01d00000

#define EDMA_RCV_PING_TCC 1

#define EDMA_RCV_PONG_TCC 2

#define EDMA_MCASPRXCH 0 // EDMA channel for McASP0 RX

#define EDMA_RCVPING 34

#define EDMA_RCVPONG 35

static Uint32 rcv_ping[BUF_LENGTH], rcv_pong[BUF_LENGTH];

void *mcasp_rcv_register = (void *)(MCASP0_BASE + 0x280);

extern void intcVectorTable(void);

CSL_McaspRegsOvly mcaspRegs = (CSL_McaspRegsOvly) CSL_MCASP_0_CTRL_REGS; //McASP0 Control Registers

CSL_AfifoRegsOvly afifoRegs = (CSL_AfifoRegsOvly) CSL_MCASP_0_FIFO_REGS; //McASP AFIFO Control Registers

CSL_AdataRegsOvly adataRegs = (CSL_AdataRegsOvly) CSL_MCASP_0_DATA_REGS; //McASP DMA Port Registers

CSL_DspintcRegsOvly intcRegs = (CSL_DspintcRegsOvly) CSL_INTC_0_REGS;

static CSL_Edma3ccRegsOvly edmaCcRegs = (CSL_Edma3ccRegsOvly)CSL_EDMA3CC_0_REGS;

void edmaInit()

{

edmaCcRegs->ECR = 0xffffffff; // clear events 0 -> 31

edmaCcRegs->SECR = 0xffffffff; // clear secondary events 0 -> 31

edmaCcRegs->IECR = 0xffffffff; // disable all interrupts

edmaCcRegs->ICR = 0xffffffff; // clear all pending interrupts

}

void edmaWritePaRAM(Int ParamNum, CSL_Edma3ccParamSetRegs *ptrParamInfo)

{

edmaCcRegs->PARAMSET[ParamNum].OPT = ptrParamInfo->OPT;

edmaCcRegs->PARAMSET[ParamNum].SRC = ptrParamInfo->SRC;

edmaCcRegs->PARAMSET[ParamNum].A_B_CNT = ptrParamInfo->A_B_CNT;

edmaCcRegs->PARAMSET[ParamNum].DST = ptrParamInfo->DST;

edmaCcRegs->PARAMSET[ParamNum].SRC_DST_BIDX = ptrParamInfo->SRC_DST_BIDX;

edmaCcRegs->PARAMSET[ParamNum].LINK_BCNTRLD = ptrParamInfo->LINK_BCNTRLD;

edmaCcRegs->PARAMSET[ParamNum].SRC_DST_CIDX = ptrParamInfo->SRC_DST_CIDX;

edmaCcRegs->PARAMSET[ParamNum].CCNT = ptrParamInfo->CCNT;

}

void setup_edma_pingpong_rcv(void *src, void *dst_ping, void *dst_pong, Uint32 acnt, Uint32 bcnt)

{

CSL_Edma3ccParamSetRegs param;

param.OPT = (EDMA_RCV_PING_TCC << 12) | (1 << 20); // transfer complete interrupt enabled

param.SRC = (Uint32)src;

param.A_B_CNT = (bcnt << 16) | acnt; // actual format: BCNT|ACNT

param.DST = (Uint32)dst_ping;

param.SRC_DST_BIDX = (acnt << 16) | 0; // actual format: DSTBIDX|SCRBIDX

param.LINK_BCNTRLD = (0 << 16) | (EDMA_RCVPONG * 0x20); // actual format: BCNTRLD|LINK

param.SRC_DST_CIDX = 0; // actual format: DSTCIDX|SRCCIDX

param.CCNT = 1;

edmaWritePaRAM(EDMA_MCASPRXCH, ¶m);

// 2. setup ping PaRAM set (to be reloaded later)

edmaWritePaRAM(EDMA_RCVPING, ¶m);

// 3. setup pong PaRAM set (to be loaded and reloaded later)

param.OPT = (EDMA_RCV_PONG_TCC << 12) | (1 << 20); // transfer complete interrupt enabled

param.LINK_BCNTRLD = (0 << 16) | (EDMA_RCVPING * 0x20); // actual format: BCNTRLD|LINK

param.DST = (Uint32)dst_pong;

edmaWritePaRAM(EDMA_RCVPONG, ¶m);

}

void EdmaIntClear(Int channelNumber)

{

edmaCcRegs->ICR = 1 << channelNumber;

}

void EdmaIntEnable(Int intNumber)

{

edmaCcRegs->IESR = 1 << intNumber;

edmaCcRegs->DRA[0].DRAE &= ~(1 << intNumber);

edmaCcRegs->DRA[1].DRAE |= 1 << intNumber;

}

void EdmaEnableChannel(Int channelNumber, Int QueueNumber)

{

int mask;

edmaCcRegs->EMCR = 1 << channelNumber;

edmaCcRegs->SECR = 1 << channelNumber;

QueueNumber &= 1; // only 0 or 1 are valid

mask = 0x07 << (4 * (channelNumber & 0x07) );

edmaCcRegs->DMAQNUM[channelNumber >> 3] &= ~mask;

edmaCcRegs->DMAQNUM[channelNumber >> 3] |= QueueNumber << (4 * (channelNumber & 0x07) );

edmaCcRegs->EESR = 1 << channelNumber;

}

void main (void)

{

/* Put McASP in Reset by programming the global control registers */

//Keep all Tx Clocks in Reset

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_XFRST, RESET);

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_XSMRST, RESET);

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_XSRCLR, CLEAR);

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_XHCLKRST, RESET);

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_XCLKRST, RESET);

//Keep all Rx Clocks In Reset

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_RFRST, RESET);

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_RSMRST, RESET);

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_RSRCLR, CLEAR);

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_RHCLKRST, RESET);

CSL_FINST(mcaspRegs->GBLCTL, MCASP_GBLCTL_RCLKRST, RESET);

CSL_FINST(afifoRegs->WFIFOCTL, AFIFO_WFIFOCTL_WENA, DISABLED); //Disable Tx FIFO

CSL_FINST(afifoRegs->RFIFOCTL, AFIFO_RFIFOCTL_RENA, DISABLED); //Disable Rx FIFO

//Configure the receive bit stream for 32 bit I2S.

CSL_FINST(mcaspRegs->RFMT, MCASP_RFMT_RDATDLY, 1BIT); //Ignore First Bit due to I2S

CSL_FINST(mcaspRegs->RFMT, MCASP_RFMT_RRVRS, MSBFIRST);

CSL_FINST(mcaspRegs->RFMT, MCASP_RFMT_RPAD, ZERO); //Pad Unused Bits with value in bit 0

CSL_FINST(mcaspRegs->RFMT, MCASP_RFMT_RSSZ, 32BITS); //32 bit slot size, though only 24 bit word size

CSL_FINST(mcaspRegs->RFMT, MCASP_RFMT_RROT, NONE); //No Rotation needed

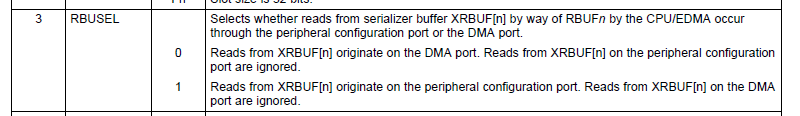

CSL_FINST(mcaspRegs->RFMT, MCASP_RFMT_RBUSEL, VBUS); //Read XRBUF[n] on the Peripheral Configuration Port (For Now -> May change to the DMA Later)

/* Recieve Format Unit Bit Mask Register */

//Mask Off Unused Bits -> For Now, well leave all unmasked -> May change later.

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK31, NOMASK); //Audio Data MSB

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK30, NOMASK); //Audio Data MSB-1

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK29, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK28, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK27, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK26, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK25, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK24, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK23, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK22, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK21, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK20, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK19, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK18, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK17, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK16, NOMASK); //Audio Data Bit LSB (16 bit)

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK15, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK14, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK13, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK12, NOMASK); //Audio Data Bit LSB (20 bit)

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK11, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK10, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK9, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK8, NOMASK); //Audio Data LSB (24 bit)

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK7, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK6, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK5, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK4, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK3, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK2, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK1, NOMASK);

CSL_FINST(mcaspRegs->RMASK, MCASP_RMASK_RMASK0, NOMASK);

/* Receive Frame Sync Control Register */

CSL_FINST(mcaspRegs->AFSRCTL, MCASP_AFSRCTL_RMOD, I2S); //Configure Frame Sync for 2 Channel TDM

CSL_FINST(mcaspRegs->AFSRCTL, MCASP_AFSRCTL_FRWID, WORD); //Configure Frame Sync to last length of word

CSL_FINST(mcaspRegs->AFSRCTL, MCASP_AFSRCTL_FSRM, EXTERNAL); //Configure Frame Sync for external generation

CSL_FINST(mcaspRegs->AFSRCTL, MCASP_AFSRCTL_FSRP, FALLINGEDGE); //Configure Frame Sync that falling edge starts new channel for I2S

/* Receive Bit Clock Control Register */

CSL_FINST(mcaspRegs->ACLKRCTL, MCASP_ACLKRCTL_CLKRP, RISINGEDGE); //Sample bit on Rising Edge of ACLKR

CSL_FINST(mcaspRegs->ACLKRCTL, MCASP_ACLKRCTL_CLKRM, EXTERNAL); //Clock Generated by codec

CSL_FINS(mcaspRegs->ACLKRCTL, MCASP_ACLKRCTL_CLKRDIV, 0); //Irrelvant when ASYNC = 0

/*Receive High Frequency Clock Control Register (Master Clock)*/

//Irrelvant when ASYNC = 0

CSL_FINST(mcaspRegs->AHCLKRCTL, MCASP_AHCLKRCTL_HCLKRM, EXTERNAL);

CSL_FINST(mcaspRegs->AHCLKRCTL, MCASP_AHCLKRCTL_HCLKRP, NOTINVERTED);

// AHCLKR = 24.576MHz

CSL_FINS(mcaspRegs->AHCLKRCTL, MCASP_AHCLKRCTL_HCLKRDIV, 0);

/*Receive TDM Time Slot Register */

//Slots 31-2 Inactive

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS31, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS30, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS29, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS28, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS27, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS26, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS25, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS24, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS23, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS22, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS21, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS20, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS19, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS18, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS17, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS16, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS15, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS14, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS13, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS12, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS11, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS10, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS9, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS8, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS7, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS6, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS5, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS4, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS3, INACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS2, INACTIVE);

//Slots 0,1 Active for I2S

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS1, ACTIVE);

CSL_FINST(mcaspRegs->RTDM, MCASP_RTDM_RTDMS0, ACTIVE);

/* Receiver Interrupt Control Register */

CSL_FINST(mcaspRegs->RINTCTL, MCASP_RINTCTL_RSTAFRM, DISABLE); //Disable Start of Frame Interrupt

CSL_FINST(mcaspRegs->RINTCTL, MCASP_RINTCTL_RDATA, DISABLE); //Disable Data Read Interrupt

CSL_FINST(mcaspRegs->RINTCTL, MCASP_RINTCTL_RLAST, DISABLE); //Disable Recive Last Time Slot Interrupt

CSL_FINST(mcaspRegs->RINTCTL, MCASP_RINTCTL_RDMAERR, DISABLE); //Disable DMA Error Interrupt

CSL_FINST(mcaspRegs->RINTCTL, MCASP_RINTCTL_RCKFAIL, DISABLE); //Disable Clock Failure Error Interrupt

CSL_FINST(mcaspRegs->RINTCTL, MCASP_RINTCTL_RSYNCERR, DISABLE); //Disable Unexpected FrameSync Error Interrupt

CSL_FINST(mcaspRegs->RINTCTL, MCASP_RINTCTL_ROVRN, DISABLE); //Disable Reciever Overrun Error Interrupt

CSL_FINST(mcaspRegs->SRCTL0, MCASP_SRCTL0_SRMOD, RCV); //Configure Serializer 0 to be a Recieve Serializer

/* PFUNC Register */

//Configure AHCLKX, ACLKX, AFSX, AXR0, AXR1 as McASP Pins vs. GPIO Pins

CSL_FINST(mcaspRegs->PFUNC, MCASP_PFUNC_AFSX, MCASP);

CSL_FINST(mcaspRegs->PFUNC, MCASP_PFUNC_AHCLKX, MCASP);

CSL_FINST(mcaspRegs->PFUNC, MCASP_PFUNC_ACLKX, MCASP);

CSL_FINST(mcaspRegs->PFUNC, MCASP_PFUNC_AXR0, MCASP);

//Configure AXR0 as Input to Get Data from PCM4220

CSL_FINST(mcaspRegs->PDIR, MCASP_PDIR_AFSR, INPUT);

CSL_FINST(mcaspRegs->PDIR, MCASP_PDIR_AHCLKR, INPUT);

CSL_FINST(mcaspRegs->PDIR, MCASP_PDIR_ACLKR, INPUT);

CSL_FINST(mcaspRegs->PDIR, MCASP_PDIR_AXR0, INPUT);

/* Digital Interface Tranmistter Control Regiser */

//Disable DIT Portion of McASP

CSL_FINST(mcaspRegs->DITCTL, MCASP_DITCTL_DITEN, DISABLE);

/* Digital Loopback Control Register*/

//Configure Digital Loopback

CSL_FINST(mcaspRegs->DLBCTL, MCASP_DLBCTL_DLBEN, DISABLE);

CSL_FINST(mcaspRegs->DLBCTL, MCASP_DLBCTL_ORD, XMTODD);

//Configure AMUTE Pin to drive when any Error Occurs

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_XDMAERR, DISABLE);

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_RDMAERR, DISABLE);

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_XCKFAIL, DISABLE);

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_RCKFAIL, DISABLE);

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_XUNDRN, DISABLE);

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_ROVRN, DISABLE);

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_XUNDRN, DISABLE);

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_ROVRN, DISABLE);

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_INSTAT, INACTIVE); //Disable AMUTEIN Pin to isolate from LogicPD HW status

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_INEN, DISABLE); //Disable Drive on AMUTEOUT when AMUTEIN error is active

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_INPOL, ACTHIGH); //Configure AMUTE Input Logic Level to High

CSL_FINST(mcaspRegs->AMUTE, MCASP_AMUTE_MUTEN, DISABLE); //Disable AMUTE PIN

if(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RHCLKRST)!=CSL_MCASP_GBLCTL_RHCLKRST_ACTIVE)

{

CSL_FINST(mcaspRegs->RGBLCTL, MCASP_RGBLCTL_RHCLKRST, ACTIVE); //Start Recieve High Frequency clock

while(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RHCLKRST)!=CSL_MCASP_GBLCTL_RHCLKRST_ACTIVE); //Stall until GBLCTL reads back to ensure it was latched by the logic

}

if(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RCLKRST)!=CSL_MCASP_GBLCTL_RCLKRST_ACTIVE){

//Start Recieve Serial Clock

CSL_FINST(mcaspRegs->RGBLCTL, MCASP_RGBLCTL_RCLKRST, ACTIVE);

//Stall until GBLCTL reads back to ensure it was latched by the logic

while(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RCLKRST)!=CSL_MCASP_GBLCTL_RCLKRST_ACTIVE);

}

mcaspRegs->RSTAT = 0x0000FFFF;

if(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RSRCLR)!=CSL_MCASP_GBLCTL_RSRCLR_ACTIVE){

//Start Recieve Serial Clock

CSL_FINST(mcaspRegs->RGBLCTL, MCASP_RGBLCTL_RSRCLR, ACTIVE);

// Stall until GBLCTL reads back to ensure it was latched by the logic

while(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RSRCLR)!=CSL_MCASP_GBLCTL_RSRCLR_ACTIVE);

}

if(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RSMRST)!=CSL_MCASP_GBLCTL_RSMRST_ACTIVE){

//Start Recieve Serial Clock

CSL_FINST(mcaspRegs->RGBLCTL, MCASP_RGBLCTL_RSMRST, ACTIVE);

// Stall until GBLCTL reads back to ensure it was latched by the logic

while(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RSMRST)!=CSL_MCASP_GBLCTL_RSMRST_ACTIVE);

}

if(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RFRST)!=CSL_MCASP_GBLCTL_RFRST_ACTIVE){

//Start Recieve Serial Clock

CSL_FINST(mcaspRegs->RGBLCTL, MCASP_RGBLCTL_RFRST, ACTIVE);

//Stall until GBLCTL reads back to ensure it was latched by the logic

while(CSL_FEXT(mcaspRegs->GBLCTL, MCASP_GBLCTL_RFRST)!=CSL_MCASP_GBLCTL_RFRST_ACTIVE);

}

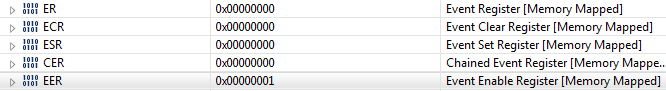

edmaInit();

setup_edma_pingpong_rcv(mcasp_rcv_register, rcv_ping, rcv_pong, BYTES_PER_SAMPLE, BUF_LENGTH);

EdmaEnableChannel(EDMA_MCASPRXCH, 0);

EdmaIntEnable(EDMA_RCV_PING_TCC);

EdmaIntEnable(EDMA_RCV_PONG_TCC);

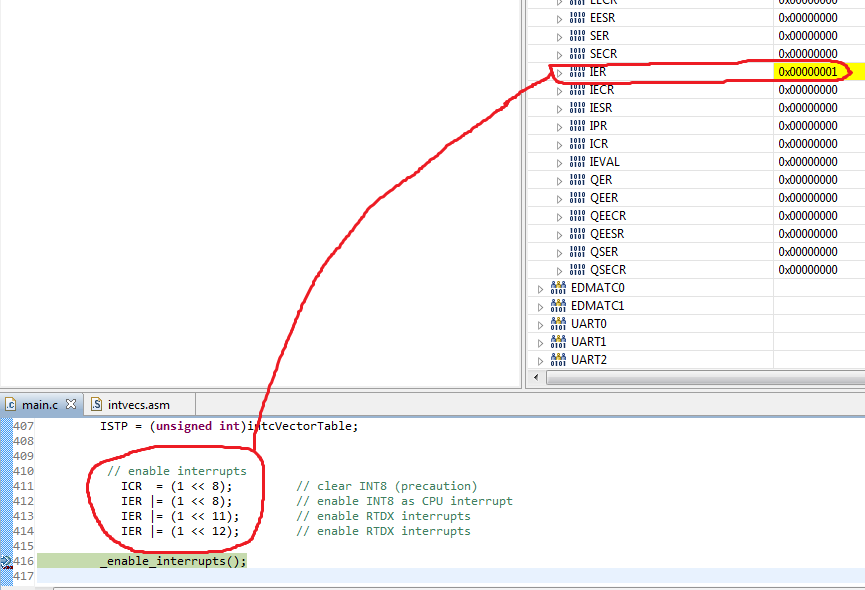

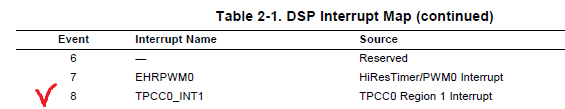

CSL_FINS(intcRegs->INTMUX2, DSPINTC_INTMUX2_INTSEL8, 8);

ISTP = (unsigned int)intcVectorTable;

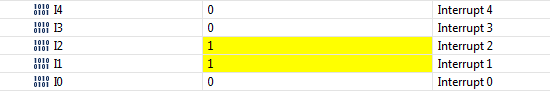

// enable interrupts

ICR = (1 << 8); // clear INT8 (precaution)

IER |= (1 << 8); // enable INT8 as CPU interrupt

IER |= (1 << 11); // enable RTDX interrupts

IER |= (1 << 12); // enable RTDX interrupts

_enable_interrupts();

while (1);

}

interrupt void EDMA3CC_INT1_isr ()

{

while(edmaCcRegs->IPR)

{

if (edmaCcRegs->IPR & (1 << EDMA_RCV_PING_TCC)) // receive channel (ping)

{

EdmaIntClear(EDMA_RCV_PING_TCC);

}

if (edmaCcRegs->IPR & (1 << EDMA_RCV_PONG_TCC)) // receive channel (pong)

{

EdmaIntClear(EDMA_RCV_PONG_TCC);

}

}

}