Hello All

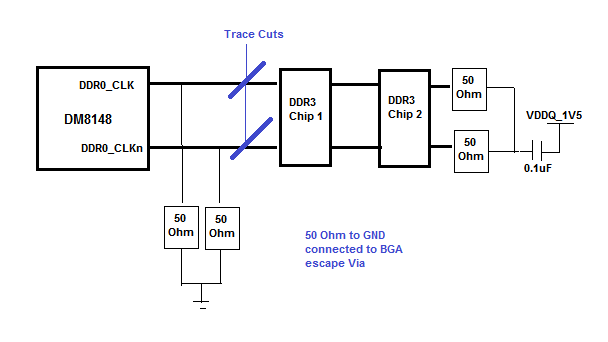

We are working on custom board using DM8148 with DDR3 chips. We make use of the DDR0 interface only.

On our prototype, on measuring the DDR Clock signal using a differential probe, we notice that there is (a) very little margin on tCH(avg) and tCL(avg) values using DDR chip for one manufacturer. (b) fail tCH(avg) and tCL(avg) measurements on measuring using our second source chip.

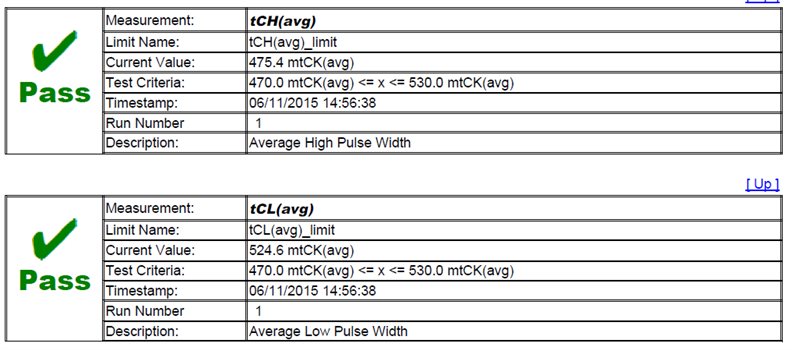

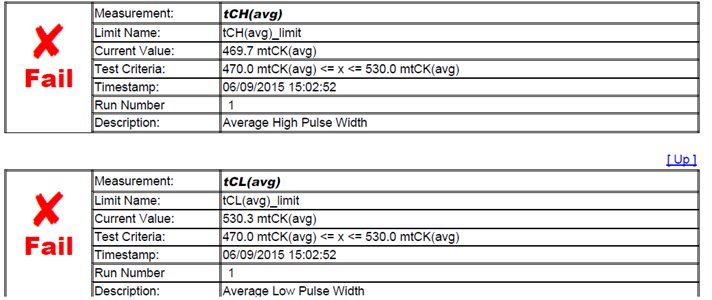

I have atatched the screenshots of the measurement data from the report.

Marginal Pass:

Failed Measurement:

Other measurements using the Test Suite from LeCroy's DDR3 measurement software look ok with sufficient margin. Both the boards are working fine and we do not have functionality issues with respect to DDR.

We used the DM814x_DDR_Controller_Register_Configuration_spreadsheet_v1.0 from TI to generate the register values. The input to the excel sheet were based on the DDR device datasheet.

Can somebody tell me which register values might need to be tweaked so as to get the correct clock signal symmetry. Does this relate to the slew rate of Clock signal?

Thanks.

Regards,

Padmanabhan