Hi,

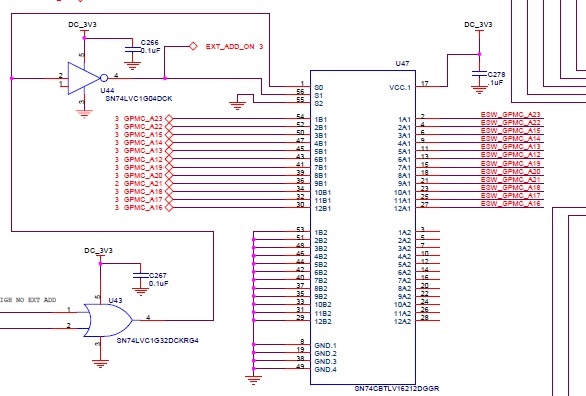

We want to interface between AM335X series processor with parallel NOR Flash from Spansion for which we have an application note attached in this email but this application note refers to OMAP35 series GPMC interface with NOR Flash.

Can we refer the same application note for AM335X series or are there some differences between AM35 and AM33 series of processors as far as GPMC or for that matter XIP interface is concerned.

Thanking you.

RegardsIface_Flash_TI_OMAP_Proc_AN.pdf

Mohit