Other Parts Discussed in Thread: TMS320C6455

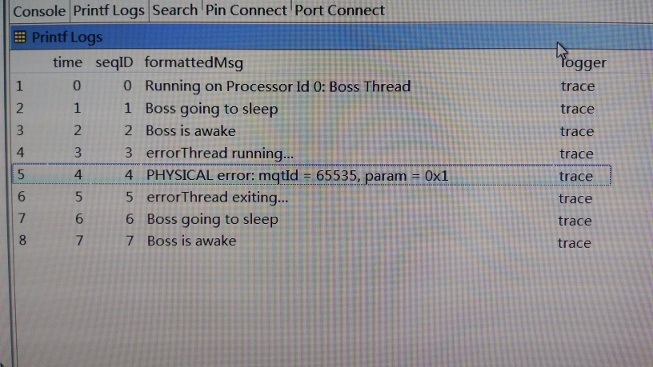

hello ,I'm debugging MQT example (SRIO) using 2 tms320c6455, and if I don't enable the L1 and L2 cache , the example can work well unconditionally , but after I enable the L1 and L2(64KB) cache, the program halt and the emulator generate a problem and disconnected with the board, after I read the guide of MQT ,I found I should rebuid the MQT lib with cache coherence operation enable, after I did that , I rebuild the program with the new MQT lib, the program didn't disconnect with the board , but it halt (stoped at UTL_halt), then I put the buffer pool that the MQT using into L2 SRAM using "#pragma DATA_SECTION" macro, the program can work well at the first time I load the program after I powered on the board, but generatea fault as bellow after the first time: