Hello,

After a few days of testing different types of configurations and a new MT9P031 sensor, i'm still not able to communicate properly with the chip, the initialization procedure it's down below.

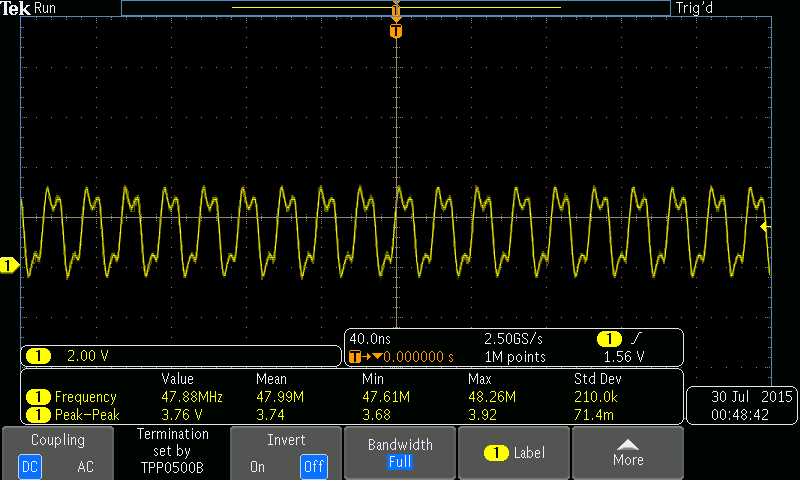

The real issue it's that i can write registers, read them back, but they are not getting updated so no effect it's generated, for example writing REG_MT9P031_PCLK_CTRL to 0x0002 (this should divide the pixel clock by 4) has no effect, measuring the pixel clock output i get 48Mhz (as the signal generator it's providing).

Also, the thing it happens if i provide a signal click between 6--27Mhz (in for PLL to work) and set the PLL registers acordingly, the clock it'c not getting divided evenso the the readed values from registers are correct.

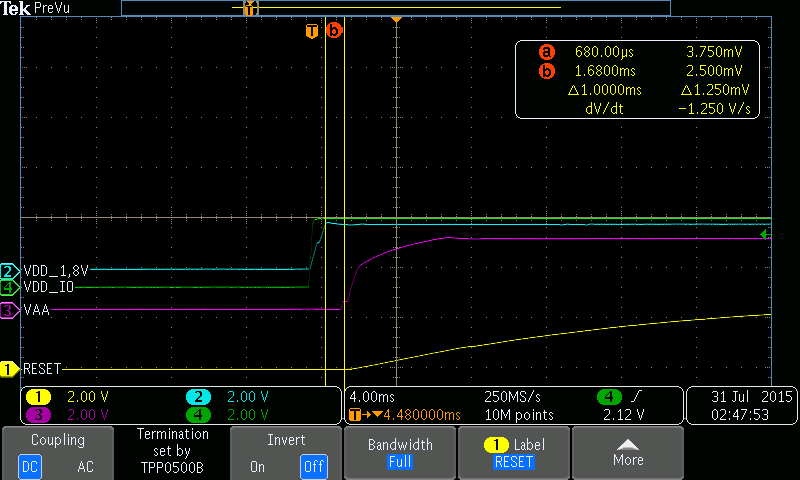

For input clock 12Mhz, should result 48Mhz.

MT9V032_writeRegister(REG_MT9P031_PLL_CTRL, 0x0002); USTIMER_delay(300000); MT9V032_writeRegister(REG_MT9P031_PLL_CONF1, 0x1002); USTIMER_delay(300000); MT9V032_writeRegister(REG_MT9P031_PLL_CONF2, 0x0002); USTIMER_delay(300000); MT9V032_writeRegister(REG_MT9P031_PLL_CTRL, 0x0003); USTIMER_delay(300000);

References:

https://www.aptina.com/assets/downloadDocument.do?id=864 registers

https://www.aptina.com/assets/downloadDocument.do?id=865 data sheet

https://www.aptina.com/products/image_sensors/mt9p031i12stc/

Reading register:

Writing register:

Pixel clock frequency:

void MT9P031_init()

{

MT9V032_writeRegister(REG_MT9P031_OUT_CTRL, 0x1F83);

USTIMER_delay(300000);

MT9V032_writeRegister(REG_MT9P031_RESTART, 0x0003);

USTIMER_delay(300000);

MT9V032_writeRegister(REG_MT9P031_PCLK_CTRL, 0x0002);

MT9V032_writeRegister(REG_MT9P031_TEST_PATTERN, 0x0011);

MT9V032_writeRegister(REG_MT9P031_GLOBAL_GAIN, 0x0008);

MT9V032_writeRegister(REG_MT9P031_READ_MODE1, 0x4006);

MT9V032_writeRegister(REG_MT9P031_ROW_ADDR_MODE, 0x0033);

MT9V032_writeRegister(REG_MT9P031_COL_ADDR_MODE, 0x0033);

MT9V032_writeRegister(REG_MT9P031_OUT_CTRL, 0x1F82);

USTIMER_delay(300000);

USTIMER_delay(300000);

USTIMER_delay(300000);

USTIMER_delay(300000);

MT9V032_writeRegister(REG_MT9P031_RESTART, 0x0001);

USTIMER_delay(300000);

USTIMER_delay(300000);

USTIMER_delay(300000);

USTIMER_delay(300000);

MT9V032_readRegister(REG_MT9P031_PCLK_CTRL, ®_u16);

printf("REG_MT9P031_PCLK_CTRL = 0x%04X\r\n",reg_u16);

MT9V032_readRegister(REG_MT9P031_RESTART, ®_u16);

printf("REG_MT9P031_RESTART = 0x%04X\r\n",reg_u16);

MT9V032_readRegister(REG_MT9P031_TEST_PATTERN, ®_u16);

printf("REG_MT9P031_TEST_PATTERN = 0x%04X\r\n",reg_u16);

MT9V032_readRegister(REG_MT9P031_OUT_CTRL, ®_u16);

printf("REG_MT9P031_OUT_CTRL = 0x%04X\r\n",reg_u16);

}

Regards,

Adrian Bostan.