Hi.

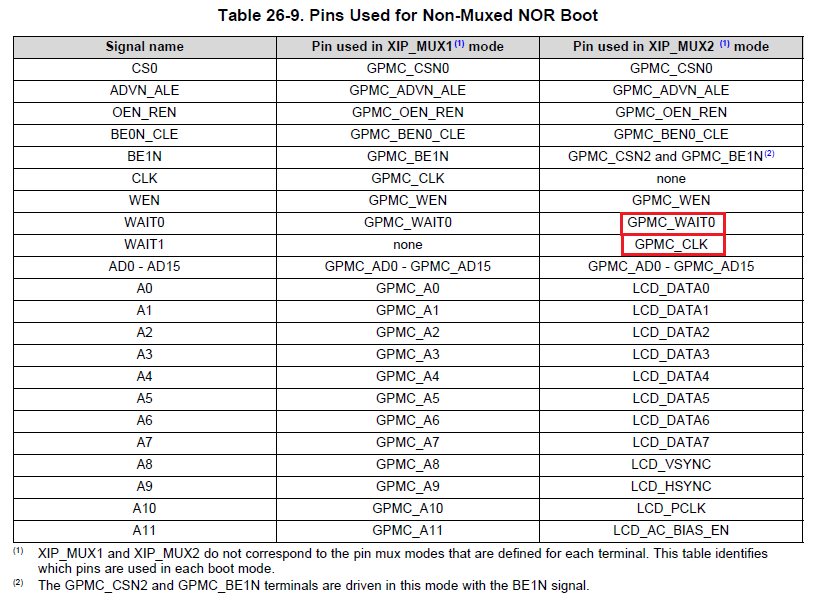

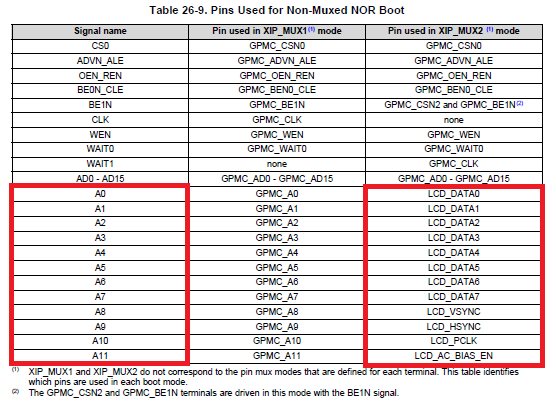

One of my customers would like to use the AM335x Non-Muxed XIP_MUX2 mode for NOR boot.

I have two questions about the WAIT pins handling for the boot.

- If we prefer the XIP with WAIT mode although we don't use the WAIT feature, do we need to pull-up both WAIT0(GPMC_WAIT0) and WAIT1(GPMC_CLK)?

- If we prefer the XIP without WAIT mode, can we use the GPMC_WAIT pin and the GPMC_CLK pin as GPIO?

(I'd like to know if the public ROM code changes the PINMUX for the WAIT pins at the XIP without WAIT mode.)

Best regards,

Tsutomu Furuse