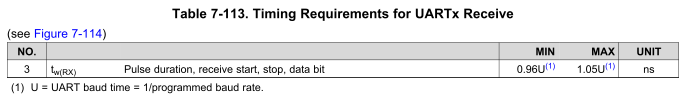

The pulse duration requirement depends on the programmed baud rate.

To receive, does a bit that is out of the pulse duration requirement fail?

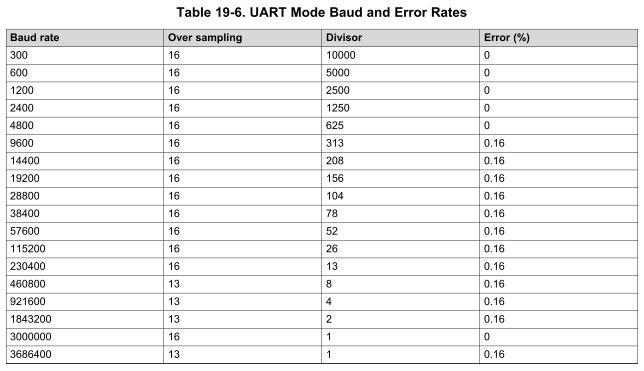

Table 19-6 on TRM (SPRUH73L) describes "Over sampling". If the over sampling is used, the pulse duration requirement should be looser. Do I misunderstand it?

Best regards,

Daisuke