Dear all,

I am working on evmc6657 board and I am going through the examples that load one simple hello word from core 0 to core 1.

I have used the code that is included in the examples under folder /srio

The main routine of this code is the following

coreNum = platform_get_coreid();

if (coreNum == 0)

{

// platform_uart_init();

// platform_uart_set_baudrate(BOOT_UART_BAUDRATE);

printf("%s%s\n\n", version_msg, version);

/* Unlock the chip registers */

DEVICE_REG32_W(KICK0, 0x83e70b13);

DEVICE_REG32_W(KICK1, 0x95a4f1e0);

/* Writing the entry address to other cores */

for (core = 1; core < NUMBER_OF_CORES; core++)

{

sprintf(boot_msg, "\r\n\r\nBooting Hello World image on Core %d from Core 0 ...", core);

printf("%s\n",boot_msg);

DEVICE_REG32_W(BOOT_MAGIC_ADDR(core), (uint32_t)write_boot_magic_number);

/* Delay 1 sec */

platform_delay(1);

}

for (core = 1; core < NUMBER_OF_CORES; core++)

{

/* IPC interrupt other cores */

DEVICE_REG32_W(IPCGR(core), 1);

platform_delay(1000);

}

}

else

{

write_boot_magic_number();

}

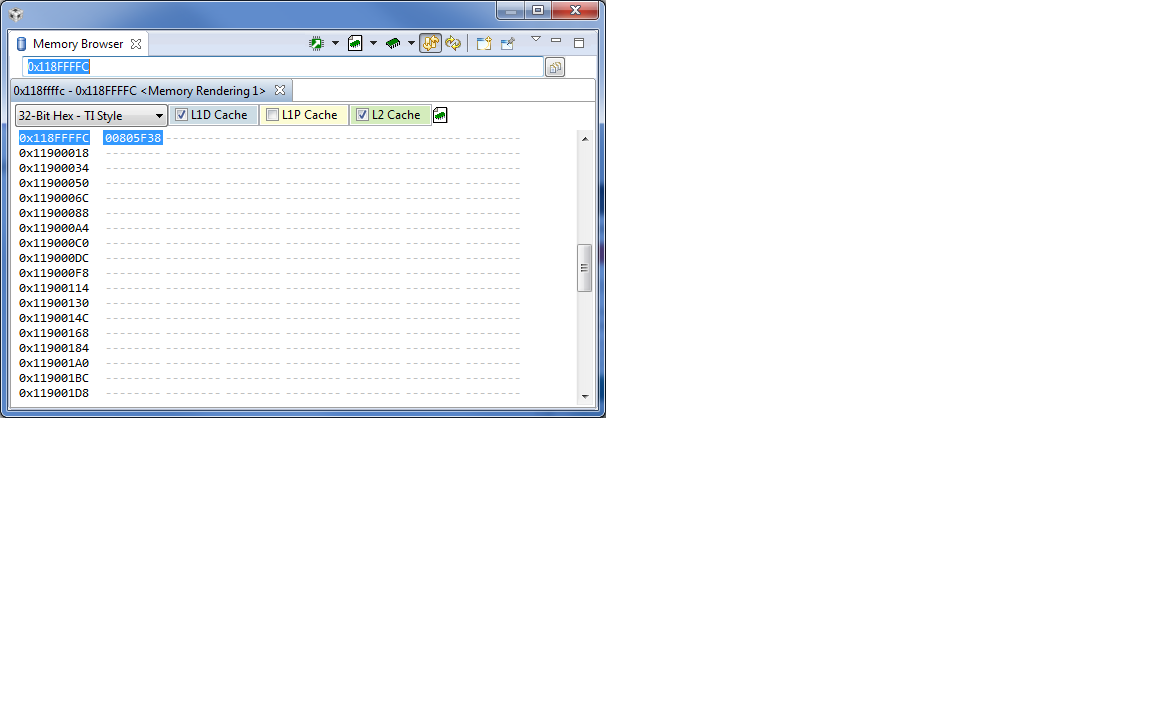

I use the CCS6 . Using the debugger I noticed that the code enters only in the the branch that is related with the core 0 and never in the branch that is related with core1. Are any additional setting that are needed to see that the second core is loaded and run?

I have removed the code for the UART. I want to test only that the code enters in the else

Best regards

George