Hi,

One of my customer wants to confirm the requirement for clock transition time of ACLKR and AFSR.

We know monotonic and faster transition time (datasheet says, upto 10ns) would be generic requirement for all clocks, but now we would like to have your comments for more specific use case.

ACLKR and AFSR are configured as output and McASP will provide the required clocks to external device such as ADC.

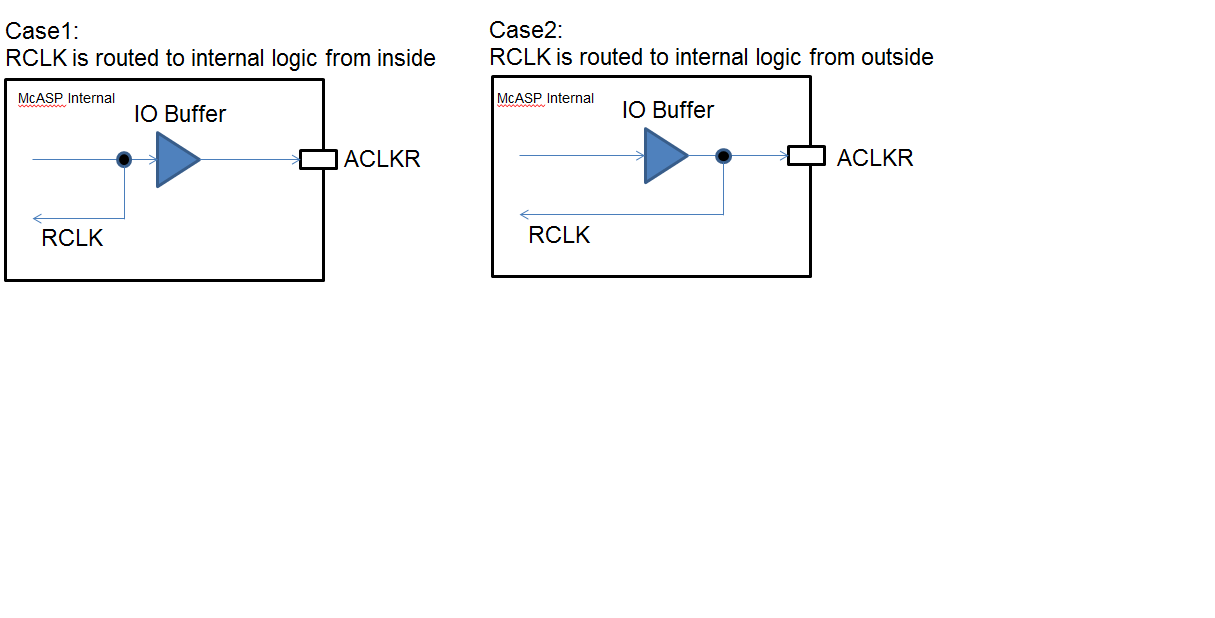

McASP samples incoming audio data with RCLK. So, McASP internal block (around IO buffer) may be looked like below:

So the first question is, which view is more proper integration for clock routing in McASP, case1 or case2 ?

So the first question is, which view is more proper integration for clock routing in McASP, case1 or case2 ?

This view is only for ACLKR, but how about AFSR ?

Our assumption is the internal block of McASP looks like case1 because it provide noise immunity in RCLK.

In fact, my customer tried to short these clock lines to GND when their system is active, and they did not see any errors such like McASP Framesync Error.

So they are wondering if the requirements for clocks (monotonic and faster transition time) are really applied to their use case.

I know such information would be restricted to TI internal, but it would be so appreciated if you could provide the comments on this.

Best Regards,

Naoki Kawada