hello guys

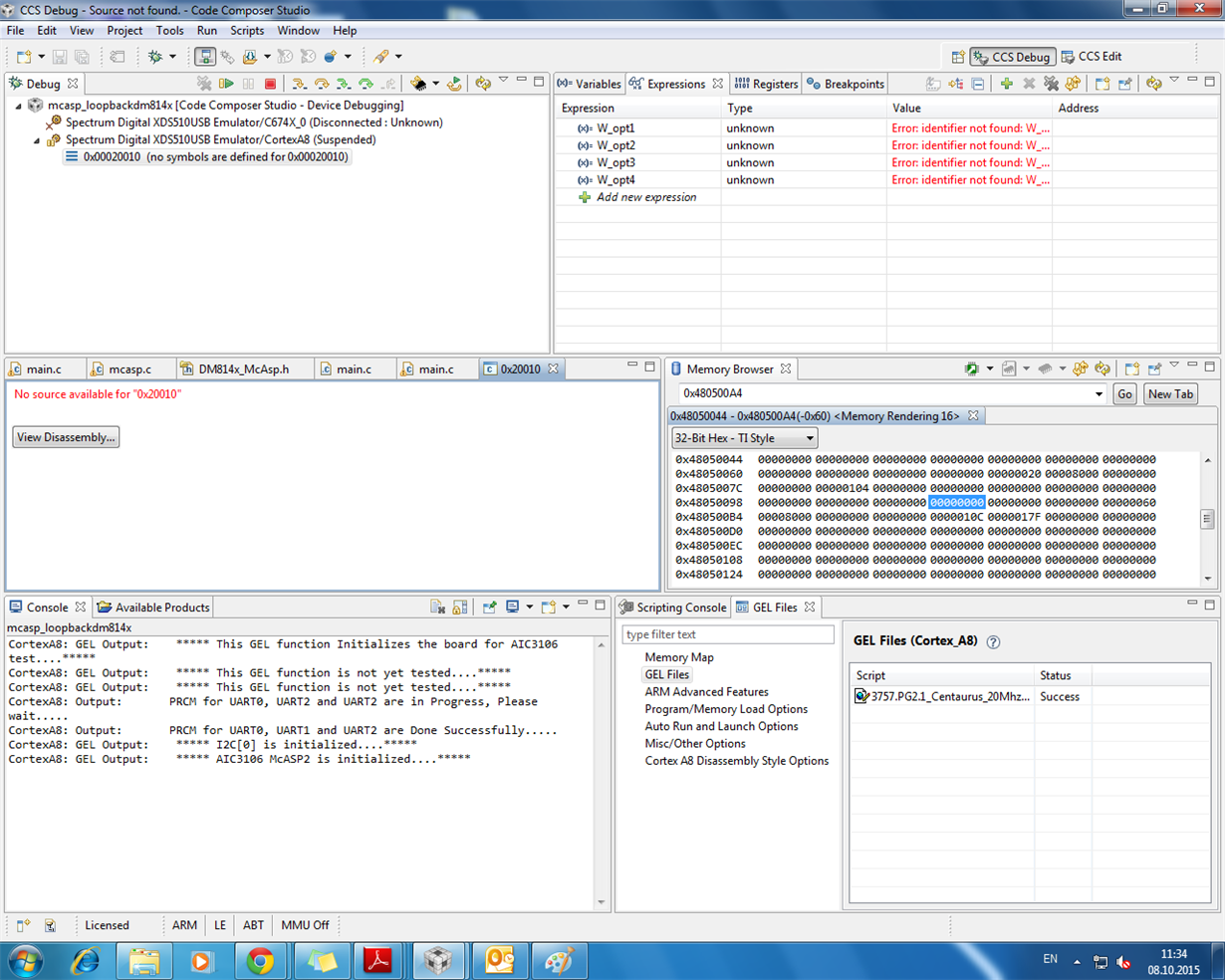

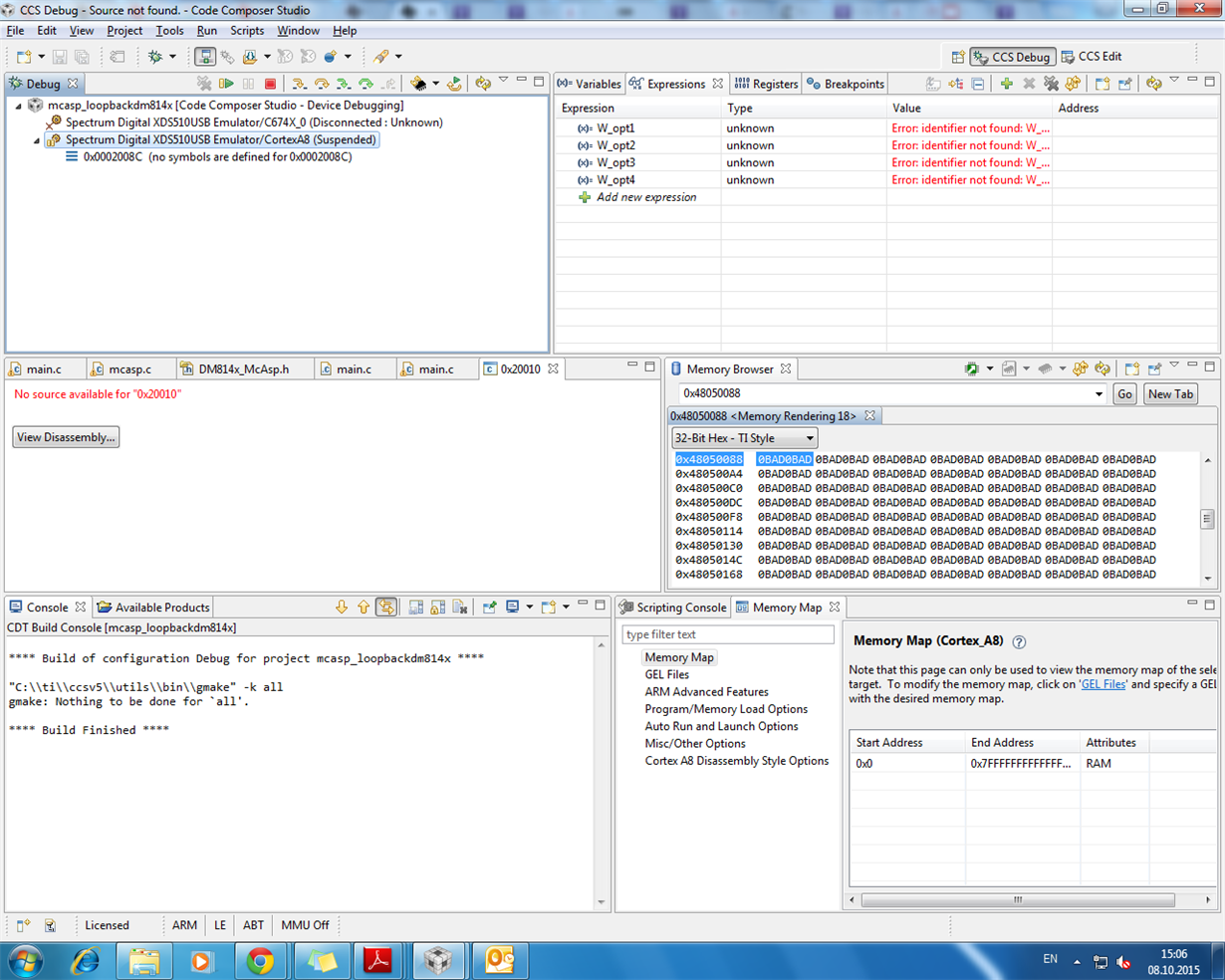

I am trying to implement simply an internal loopback test on mcasp dm814x using code composer ccs5 .Although registers are configured properly but still it shows ambiguites nd test jumps to nowhere stating "no source available for 0x20010. I have tried many times to pinpoint the fault but i think few bits of GBLCTL are not configured.Though i took this configuration from Mistral test codes and using gel file for initializing clocks but its not going anywhere except "no source available "i am pasting test code here.kindly help me in this regards.

//declarations//

#define DM814X_MCASP0_BASE (0x48038000u)

/**< McASP 0 Base address */

#define DM814X_MCASP1_BASE (0x4803C000u)

/**< McASP 1 Base address */

#define DM814X_MCASP2_BASE (0x48050000u)

/**< McASP 2 Base address */

#define DM814X_MCASP3_BASE (0x4A1A2000u)

/**< McASP 3 Base address */

#define DM814X_MCASP4_BASE (0x4A1A8000u)

/**< McASP 4 Base address */

#define DM814X_MCASP5_BASE (0x4A1AE000u)

/**< McASP 5 Base address */

#define MCASP_PID_OFFSET (0x00000000u)

/**< Offset of the Peripheral ID register */

#define MCASP_PWRIDLESYSCONFIG_OFFSET (0x00000004u)

/**< Offset of the Power IDLE SYSCONFIG register */

#define MCASP_PFUNC_OFFSET (0x00000010u)

/**< Offset of the Pin Function Control register */

#define MCASP_PDIR_OFFSET (0x00000014u)

/**< Offset of the Pin Direction Control register */

#define MCASP_PDOUT_OFFSET (0x00000018u)

/**< Offset of the Pin Data out register */

#define MCASP_PDSET_OFFSET (0x0000001Cu)

/**< Offset of the Pin Data Set register */

#define MCASP_PDCLR_OFFSET (0x00000020u)

/**< Offset of the Pin Data Clear register */

#define MCASP_GBLCTL_OFFSET (0x00000044u)

/**< Offset of the Global Control register */

#define MCASP_AMUTE_OFFSET (0x00000048u)

/**< Offset of the Audio Mute Control register */

#define MCASP_DLBCTL_OFFSET (0x0000004Cu)

/**< Offset of the Loop Back test Control register */

#define MCASP_DITCTL_OFFSET (0x00000050u)

/**< Offset of the Transmit DIT Mode Control register */

#define MCASP_RGBLCTL_OFFSET (0x00000060u)

/**< Offset of the Global Control register alias for Receiver */

#define MCASP_RMASK_OFFSET (0x00000064u)

/**< Offset of the Receiver Mask register */

#define MCASP_RFMT_OFFSET (0x00000068u)

/**< Offset of the Receive Format Control register */

#define MCASP_AFSRCTL_OFFSET (0x0000006Cu)

/**< Offset of the Frame Sync Control register for Receiver */

#define MCASP_ACLKRCTL_OFFSET (0x00000070u)

/**< Offset of the Receive Clock Control register */

#define MCASP_AHCLKRCTL_OFFSET (0x00000074u)

/**< Offset of the High frequency Receive Clock conrol register */

#define MCASP_RTDM_OFFSET (0x00000078u)

/**< Offset of the TDM Slot for Receive */

#define MCASP_RINTCTL_OFFSET (0x0000007Cu)

/**< Offset of the Receive Event Clear register */

#define MCASP_RSTAT_OFFSET (0x00000080u)

/**< Offset of the Receive Status register */

#define MCASP_RSLOT_OFFSET (0x00000084u)

/**< Offset of the Current active Receive TDM Slot register */

#define MCASP_RCLKCHK_OFFSET (0x00000088u)

/**< Offset of the Receive Clock check control register */

#define MCASP_REVTCTL_OFFSET (0x00000088u)

/**< Offset of the Receive DMA Event register */

#define MCASP_XGBLCTL_OFFSET (0x000000A0u)

/**< Offset of the Transmit Global Control register */

#define MCASP_XMASK_OFFSET (0x000000A4u)

/**< Offset of the Transmit Mask register */

#define MCASP_XFMT_OFFSET (0x000000A8u)

/**< Offset of the Transmit Fromat Control register */

#define MCASP_AFSXCTL_OFFSET (0x000000ACu)

/**< Offset of the Transmit Frame Sync Control register */

#define MCASP_ACLKXCTL_OFFSET (0x000000B0u)

/**< Offset of the Transmit Clock Control register */

#define MCASP_AHCLKXCTL_OFFSET (0x000000B4u)

/**< Offset of the Transmit High freq clock Control register */

#define MCASP_XTDM_OFFSET (0x000000B8u)

/**< Offset of the Transmit TDM slot control register */

#define MCASP_XINTCTL_OFFSET (0x000000BCu)

/**< Offset of the Transmit Interrupt Control register */

#define MCASP_XSTAT_OFFSET (0x000000C0u)

/**< Offset of the Transmit status register */

#define MCASP_XSLOT_OFFSET (0x000000C4u)

/**< Offset of the Current active Transmit TDM slot register */

#define MCASP_XCLKCHK_OFFSET (0x000000C4u)

/**< Offset of the Transmit Clock check register */

//MCASP2 Direct Declarations

#define MCASP2_PID 0x48050000

/**< Offset of the Peripheral ID register */

#define MCASP2_PWRIDLESYSCONFIG 0x48050004

/**< Offset of the Power IDLE SYSCONFIG register */

#define MCASP2_PFUNC 0x48050010

/**< Offset of the Pin Function Control register */

#define MCASP2_PDIR 0x48050014

/**< Offset of the Pin Direction Control register */

#define MCASP2_PDOUT 0x48050018

/**< Offset of the Pin Data out register */

#define MCASP2_PDIN 0x4805001C

#define MCASP2_PDSET 0x4805001C

/**< Offset of the Pin Data Set register */

#define MCASP2_PDCLR 0x48050020

/**< Offset of the Pin Data Clear register */

#define MCASP2_GBLCTL 0x48050044

/**< Offset of the Global Control register */

#define MCASP2_AMUTE 0x48050048

/**< Offset of the Audio Mute Control register */

#define MCASP2_DLBCTL 0x4805004C

/**< Offset of the Loop Back test Control register */

#define MCASP2_DITCTL 0x48050050

/**< Offset of the Transmit DIT Mode Control register */

#define MCASP2_RGBLCTL 0x48050060

/**< Offset of the Global Control register alias for Receiver */

#define MCASP2_RMASK 0x48050064

/**< Offset of the Receiver Mask register */

#define MCASP2_RFMT 0x48050068

/**< Offset of the Receive Format Control register */

#define MCASP2_AFSRCTL 0x4805006C

/**< Offset of the Frame Sync Control register for Receiver */

#define MCASP2_ACLKRCTL 0x48050070

/**< Offset of the Receive Clock Control register */

#define MCASP2_AHCLKRCTL 0x48050074

/**< Offset of the High frequency Receive Clock conrol register */

#define MCASP2_RTDM 0x48050078

/**< Offset of the TDM Slot for Receive */

#define MCASP2_RINTCTL 0x4805007C

/**< Offset of the Receive Event Clear register */

#define MCASP2_RSTAT 0x48050080

/**< Offset of the Receive Status register */

#define MCASP2_RSLOT 0x48050084

/**< Offset of the Current active Receive TDM Slot register */

#define MCASP2_RCLKCHK 0x48050088

/**< Offset of the Receive Clock check control register */

#define MCASP2_REVTCTL 0x4805008C

/**< Offset of the Receive DMA Event register */

#define MCASP2_XGBLCTL 0x480500A0

/**< Offset of the Transmit Global Control register */

#define MCASP2_XMASK 0x480500A4

/**< Offset of the Transmit Mask register */

#define MCASP2_XFMT 0x480500A8

/**< Offset of the Transmit Fromat Control register */

#define MCASP2_AFSXCTL 0x480500AC

/**< Offset of the Transmit Frame Sync Control register */

#define MCASP2_ACLKXCTL 0x480500B0

/**< Offset of the Transmit Clock Control register */

#define MCASP2_AHCLKXCTL 0x480500B4

/**< Offset of the Transmit High freq clock Control register */

#define MCASP2_XTDM 0x480500B8

/**< Offset of the Transmit TDM slot control register */

#define MCASP2_XINTCTL 0x480500BC

/**< Offset of the Transmit Interrupt Control register */

#define MCASP2_XSTAT 0x480500C0

/**< Offset of the Transmit status register */

#define MCASP2_XSLOT 0x480500C4

/**< Offset of the Current active Transmit TDM slot register */

#define MCASP2_XCLKCHK 0x480500C8

/**< Offset of the Transmit Clock check register */

#define MCASP2_XEVTCTL 0x480500CC

#define MCASP2_CLKADJEN 0x480500D0

#define MCASP2_DITCSRA0 0x48050100

#define MCASP2_DITCSRA1 0x48050104

#define MCASP2_DITCSRA2 0x48050108

#define MCASP2_DITCSRA3 0x4805010C

#define MCASP2_DITCSRA4 0x48050110

#define MCASP2_DITCSRA5 0x48050114

#define MCASP2_DITCSRB0 0x48050118

#define MCASP2_DITCSRB1 0x4805011C

#define MCASP2_DITCSRB2 0x48050120

#define MCASP2_DITCSRB3 0x48050124

#define MCASP2_DITCSRB4 0x48050128

#define MCASP2_DITCSRB5 0x4805012C

#define MCASP2_DITUDRA0 0x48050130

#define MCASP2_DITUDRA1 0x48050134

#define MCASP2_DITUDRA2 0x48050138

#define MCASP2_DITUDRA3 0x4805013C

#define MCASP2_DITUDRA4 0x48050140

#define MCASP2_DITUDRA5 0x48050144

#define MCASP2_DITUDRB0 0x48050148

#define MCASP2_DITUDRB1 0x4805014C

#define MCASP2_DITUDRB2 0x48050150

#define MCASP2_DITUDRB3 0x48050154

#define MCASP2_DITUDRB4 0x48050158

#define MCASP2_DITUDRB5 0x4805015C

#define MCASP2_XRSRCTL0 0x48050180

#define MCASP2_XRSRCTL1 0x48050184

#define MCASP2_XRSRCTL2 0x48050188

#define MCASP2_XRSRCTL3 0x4805018C

#define MCASP2_XRSRCTL4 0x48050190

#define MCASP2_XRSRCTL5 0x48050194

#define MCASP2_XRSRCTL6 0x48050198

#define MCASP2_XRSRCTL7 0x4805019C

#define MCASP2_XRSRCTL8 0x480501A0

#define MCASP2_XRSRCTL9 0x480501A4

#define MCASP2_XRSRCTL10 0x480501A8

#define MCASP2_XRSRCTL11 0x480501AC

#define MCASP2_XRSRCTL12 0x480501B0

#define MCASP2_XRSRCTL13 0x480501B4

#define MCASP2_XRSRCTL14 0x480501B8

#define MCASP2_XRSRCTL15 0x480501BC

#define MCASP2_TXBUF0 0x48050200

#define MCASP2_TXBUF1 0x48050204

#define MCASP2_TXBUF2 0x48050208

#define MCASP2_TXBUF3 0x4805020C

#define MCASP2_TXBUF4 0x48050210

#define MCASP2_TXBUF5 0x48050214

#define MCASP2_TXBUF6 0x48050218

#define MCASP2_TXBUF7 0x4805021C

#define MCASP2_TXBUF8 0x48050220

#define MCASP2_TXBUF9 0x48050224

#define MCASP2_TXBUF10 0x48050228

#define MCASP2_TXBUF11 0x4805022C

#define MCASP2_TXBUF12 0x48050230

#define MCASP2_TXBUF13 0x48050234

#define MCASP2_TXBUF14 0x48050238

#define MCASP2_TXBUF15 0x4805023C

#define MCASP2_RXBUF0 0x48050280

#define MCASP2_RXBUF1 0x48050284

#define MCASP2_RXBUF2 0x48050288

#define MCASP2_RXBUF3 0x4805028C

#define MCASP2_RXBUF4 0x48050290

#define MCASP2_RXBUF5 0x48050294

#define MCASP2_RXBUF6 0x48050298

#define MCASP2_RXBUF7 0x4805029C

#define MCASP2_RXBUF8 0x480502A0

#define MCASP2_RXBUF9 0x480502A4

#define MCASP2_RXBUF10 0x480502A8

#define MCASP2_RXBUF11 0x480502AC

#define MCASP2_RXBUF12 0x480502B0

#define MCASP2_RXBUF13 0x480502B4

#define MCASP2_RXBUF14 0x480502B8

#define MCASP2_RXBUF15 0x480502BC

/* ------------------------------------------------------------------------ *

* GBLCTL_ Field Definitions *

* ------------------------------------------------------------------------ */

#define GBLCTL_XFRST_ON 0x1000

#define GBLCTL_XSMRST_ON 0x0800

#define GBLCTL_XSRCLR_ON 0x0400

#define GBLCTL_XHCLKRST_ON 0x0200

#define GBLCTL_XCLKRST_ON 0x0100

#define GBLCTL_RFRST_ON 0x0010

#define GBLCTL_RSMRST_ON 0x0008

#define GBLCTL_RSRCLR_ON 0x0004

#define GBLCTL_RHCLKRST_ON 0x0002

#define GBLCTL_RCLKRST_ON 0x0001

#define DLBCTL_DLBEN_ON 0x0001

#define DLBCTL_ORD_ON 0x0003 //odd serializers

#define DLBCTL_ORD_OFF 0x0001 // even serializers

/*

*====================

* Structures

*====================

*/

/**

* \brief Register Overlay structure for McASP registers

*

* Register Overlay structure for McASP registers

*/

typedef struct

{

UINT32 u32REVID; /**< Revision ID for the peripheral */

UINT32 u32PWRIDLESYSCON; /**< Power Idle sys config register */

UINT32 u32Reserved008;

UINT32 u32Reserved00c;

UINT32 u32PINFUNC; /**< Pin function contrl register */

UINT32 u32PDIR; /**< Pin direction control register */

UINT32 u32PDOUT; /**< Pin data output register */

UINT32 u32PDSET; /**< Pin Data set register */

UINT32 u32PDCLR; /**< Pin data clear regisger */

UINT32 u32Reserved024;

UINT32 u32Reserved028;

UINT32 u32Reserved02C;

UINT32 u32Reserved030;

UINT32 u32Reserved034;

UINT32 u32Reserved038;

UINT32 u32Reserved03C;

UINT32 u32Reserved040;

UINT32 u32GBLCTL; /**< Global Control register */

UINT32 u32AMUTE; /**< AMUTE control register */

UINT32 u32DLBCTL; /**< Digital Loop-back mode test register */

UINT32 u32DITCTL; /**< Transmit DIT mode control register */

UINT32 u32Reserved054;

UINT32 u32Reserved058;

UINT32 u32Reserved05C;

UINT32 u32RGBLCTL; /**< Receive Global control register */

UINT32 u32RMASK; /**< Recieve Mask register */

UINT32 u32RFMT; /**< Receive Fromat regisetr */

UINT32 u32AFSRCTL; /**< Receive Frame Sync control register */

UINT32 u32ACLKRCTL; /**< Receive Clock control register */

UINT32 u32AHCLKRCTL; /**< Receive High freq Clock control register */

UINT32 u32RTDM; /**< Receive TDM Slot 0-31 register */

UINT32 u32RINTCTL; /**< Receive Event clear register*/

UINT32 u32RSTAT; /**< Receive Status register */

UINT32 u32RSLOT; /**< Receive Slot register */

UINT32 u32RCLKCHK;

UINT32 u32REVTCTL;

UINT32 u32Reserved090;

UINT32 u32Reserved094;

UINT32 u32Reserved098;

UINT32 u32Reserved09C;

UINT32 u32XGBLCTL;

UINT32 u32XMASK;

UINT32 u32XFMT;

UINT32 u32AFSXCTL;

UINT32 u32ACLKXCTL;

UINT32 u32AHCLKXCTL;

UINT32 u32XTDM;

UINT32 u32XINTCTL;

UINT32 u32XSTAT;

UINT32 u32XSLOT;

UINT32 u32XCLKCHK;

UINT32 u32XEVTCTL;

UINT32 u32Reserved0D0_0FC[44];

UINT32 u32SRCTL0;

UINT32 u32SRCTL1;

UINT32 u32SRCTL2;

UINT32 u32SRCTL3;

UINT32 u32SRCTL4;

UINT32 u32SRCTL5;

UINT32 u32SRCTL6;

UINT32 u32SRCTL7;

UINT32 u32SRCTL8;

UINT32 u32SRCTL9;

UINT32 u32SRCTL10;

UINT32 u32SRCTL11;

UINT32 u32SRCTL12;

UINT32 u32SRCTL13;

UINT32 u32SRCTL14;

UINT32 u32SRCTL15;

UINT32 u32Reserved1C0_1FC[16];

UINT32 u32XBUF0;

UINT32 u32XBUF1;

UINT32 u32XBUF2;

UINT32 u32XBUF3;

UINT32 u32XBUF4;

UINT32 u32XBUF5;

UINT32 u32XBUF6;

UINT32 u32XBUF7;

UINT32 u32XBUF8;

UINT32 u32XBUF9;

UINT32 u32XBUF10;

UINT32 u32XBUF11;

UINT32 u32XBUF12;

UINT32 u32XBUF13;

UINT32 u32XBUF14;

UINT32 u32XBUF15;

UINT32 u32Reserved240_27C[16];

UINT32 u32RBUF0;

UINT32 u32RBUF1;

UINT32 u32RBUF2;

UINT32 u32RBUF3;

UINT32 u32RBUF4;

UINT32 u32RBUF5;

UINT32 u32RBUF6;

UINT32 u32RBUF7;

UINT32 u32RBUF8;

UINT32 u32RBUF9;

UINT32 u32RBUF10;

UINT32 u32RBUF11;

UINT32 u32RBUF12;

UINT32 u32RBUF13;

UINT32 u32RBUF14;

UINT32 u32RBUF15;

} _DM814x_MCASP_REGS_, *DM814x_MCASP_REGS;

void init_MCASP_global(DM814x_MCASP_REGS stMcAspRegs)

{

//STATUS u32RetVal = SUCCESS;

//DM814x_MCASP_REGS stMcAspRegs = NULL;

// UINT16 u16Sample = 0;

// UINT16 u16MilliSec = 0;

// UINT16 u16Seconds = 0;

// UINT32 u32SampleData = 0;

/* Rx side initialization */

stMcAspRegs->u32RMASK = 0xFFFFFFFF; // No padding used

stMcAspRegs->u32RFMT = 0x00018078; // MSB 16bit, 1-delay, no pad, CFGBus

stMcAspRegs->u32AFSRCTL = 0x00000112; // 2TDM, 1bit Rising, INTERNAL FS, word

stMcAspRegs->u32ACLKRCTL = 0x000000AF; // Rising INTERNAL CLK (from tx side)

stMcAspRegs->u32AHCLKRCTL = 0x00000000; // INT CLK (from tx side)

stMcAspRegs->u32RTDM = 0x00000003; // Slots 0,1

stMcAspRegs->u32RINTCTL = 0x00000000; // Not used

stMcAspRegs->u32RCLKCHK = 0x00FF0008; // 255-MAX 0-MIN, div-by-256

/* TX */

stMcAspRegs->u32XMASK = 0xffffffff; // No padding used

stMcAspRegs->u32XFMT = 0x00018078; // MSB 16bit, 1-delay, no pad, CFGBus

stMcAspRegs->u32AFSXCTL = 0x00000110; // 2TDM, 1bit Rising edge INTERNAL FS, word

stMcAspRegs->u32ACLKXCTL = 0x00000080; // ASYNC, Rising INTERNAL CLK, div-by-16

stMcAspRegs->u32AHCLKXCTL = 0x00000000; // EXTERNAL CLK, div-by-1

stMcAspRegs->u32XTDM = 0x00000003; // Slots 0,1

stMcAspRegs->u32XINTCTL = 0x00000000; // Not used

stMcAspRegs->u32XCLKCHK = 0x00FF0008; // 255-MAX 0-MIN, div-by-256

stMcAspRegs->u32SRCTL0 = 0x000D; // MCASP2.AXR0 --> DIN

stMcAspRegs->u32SRCTL1 = 0x000E; // MCASP2.AXR1 <-- DOUT

stMcAspRegs->u32PINFUNC = 0; // All MCASPs

stMcAspRegs->u32PDIR = 0x00000001; // All inputs except AXR0, ACLKX1, AFSX1,

stMcAspRegs->u32DITCTL = 0x00000000; // Not used

stMcAspRegs->u32DLBCTL = 0x00000000; // Not used

stMcAspRegs->u32AMUTE = 0x00000000; // Not used

/* Starting sections of the McASP*/

stMcAspRegs->u32XGBLCTL |= GBLCTL_XHCLKRST_ON; // HS Clk

while ( ( stMcAspRegs->u32XGBLCTL & GBLCTL_XHCLKRST_ON ) != GBLCTL_XHCLKRST_ON );

stMcAspRegs->u32RGBLCTL |= GBLCTL_RHCLKRST_ON; // HS Clk

while ( ( stMcAspRegs->u32RGBLCTL & GBLCTL_RHCLKRST_ON ) != GBLCTL_RHCLKRST_ON );

stMcAspRegs->u32XGBLCTL |= GBLCTL_XCLKRST_ON; // Clk

while ( ( stMcAspRegs->u32XGBLCTL & GBLCTL_XCLKRST_ON ) != GBLCTL_XCLKRST_ON );

stMcAspRegs->u32RGBLCTL |= GBLCTL_RCLKRST_ON; // Clk

while ( ( stMcAspRegs->u32RGBLCTL & GBLCTL_RCLKRST_ON ) != GBLCTL_RCLKRST_ON );

stMcAspRegs->u32XSTAT = 0x0000ffff; // Clear all

stMcAspRegs->u32RSTAT = 0x0000ffff; // Clear all

stMcAspRegs->u32XGBLCTL |= GBLCTL_XSRCLR_ON; // Serialize

while ( ( stMcAspRegs->u32XGBLCTL & GBLCTL_XSRCLR_ON ) != GBLCTL_XSRCLR_ON );

stMcAspRegs->u32RGBLCTL |= GBLCTL_RSRCLR_ON; // Serialize

while ( ( stMcAspRegs->u32RGBLCTL & GBLCTL_RSRCLR_ON ) != GBLCTL_RSRCLR_ON );

/* Write a 0, so that no underrun occurs after releasing the state machine */

stMcAspRegs->u32XBUF0 = 0;

//MCASP2_RBUF0 = 0;

stMcAspRegs->u32XGBLCTL |= GBLCTL_XSMRST_ON; // State Machine

while ( ( stMcAspRegs->u32XGBLCTL & GBLCTL_XSMRST_ON ) != GBLCTL_XSMRST_ON );

stMcAspRegs->u32RGBLCTL |= GBLCTL_RSMRST_ON; // State Machine

while ( ( stMcAspRegs->u32RGBLCTL & GBLCTL_RSMRST_ON ) != GBLCTL_RSMRST_ON );

stMcAspRegs->u32XGBLCTL |= GBLCTL_XFRST_ON; // Frame Sync

while ( ( stMcAspRegs->u32XGBLCTL & GBLCTL_XFRST_ON ) != GBLCTL_XFRST_ON );

stMcAspRegs->u32RGBLCTL |= GBLCTL_RFRST_ON; // Frame Sync

while ( ( stMcAspRegs->u32RGBLCTL & GBLCTL_RFRST_ON ) != GBLCTL_RFRST_ON );

/* Start by sending a dummy write */

while( ! ( stMcAspRegs->u32SRCTL0 & 0x10 ) ); // Check for Tx ready

stMcAspRegs->u32XBUF0 = 0;//mcasp initialization//

if( DLBCTL_ORD_ON == 1 && DLBCTL_DLBEN_ON == 1 ){

printf("*\n writing data on even serializers*\n");

WR_MEM_8(stMcAspRegs->u32XBUF0,0xAA);

WR_MEM_8(stMcAspRegs->u32XBUF2,0xAA);

WR_MEM_8(stMcAspRegs->u32XBUF4,0xAA);

WR_MEM_8(stMcAspRegs->u32XBUF6,0xAA);

WR_MEM_8(stMcAspRegs->u32XBUF8,0xAA);

WR_MEM_8(stMcAspRegs->u32XBUF10,0xAA);

WR_MEM_8(stMcAspRegs->u32XBUF12,0xAA);

WR_MEM_8(stMcAspRegs->u32XBUF14,0xAA);

;

}

else if (DLBCTL_ORD_OFF == 0 && DLBCTL_DLBEN_ON ==1){

printf("\n writing data on odd serializers");

WR_MEM_8(stMcAspRegs->u32XBUF1 ,0xBB);

WR_MEM_8(stMcAspRegs->u32XBUF3 ,0xBB);

WR_MEM_8(stMcAspRegs->u32XBUF5 ,0xBB);

WR_MEM_8(stMcAspRegs->u32XBUF7 ,0xBB);

WR_MEM_8(stMcAspRegs->u32XBUF9 ,0xBB);

WR_MEM_8(stMcAspRegs->u32XBUF11 ,0xBB);

WR_MEM_8(stMcAspRegs->u32XBUF13 ,0xBB);

WR_MEM_8(stMcAspRegs->u32XBUF15 ,0);

}