Hi,

On trying to get mcasp3 to work I am having difficulties.

I have tried many options but all failed..... I don't have MCLK output from mcasp3 AHCLKX pin and I don't understand why....

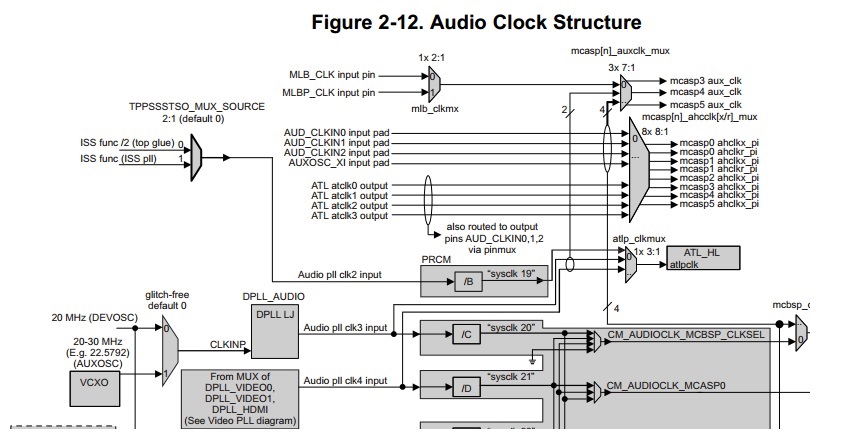

mcasp2 is getting auxosc->sysclk20->mcasp2_ahclk and it works OK. now I just wanted to add auxosc->mcasp3_ahclk

(

mcasp2_ahclk was added with:

clkp_audio_pll = clk_get(NULL,"audio_dpll_clkin_ck");

ret = clk_set_parent(clkp_audio_pll, clkp_osc1);

clk_put(clkp_audio_pll) ;

)

1. I have verificed that I use the correct pinmux for mcasp3:

MUX_VAL(PINCNTL14, (IEN | IPD | FCN4)) /* MCA[3]_AHCLKX */

2. I have tried to change clocks814_data.c default for mcasp3 parent as following:

static const struct clksel mcasp0to6_auxclk_mux_sel[] = {

{ .parent = &mcasp_auxclk_mux0_ck, .rates = div_1_0_rates },

{ .parent = &audio_dpll_ck, .rates = div_1_1_rates },

{ .parent = &video012_dpll_muxout_ck, .rates = div_1_2_rates },

old: { .parent = &xref0_ck, .rates = div_1_3_rates }, <-- what is xref0? Can't find it in pll audio schema !

new: { .parent = &audio_dpll_ck, .rates = div_1_1_rates },

{ .parent = &xref1_ck, .rates = div_1_4_rates },

{ .parent = &xref2_ck, .rates = div_1_5_rates },

{ .parent = &osc1_xi_ck, .rates = div_1_6_rates },

{ .parent = NULL}

no clock in mcasp3 AHCLKX

};

3. I have tried to set registers directly, but on reading them I get that value is 0

ioaddr2 = ioremap_nocache(0x481c6000, SZ_1K);

printk("ioaddr2 0x%lx\n",ioaddr2);

*(( unsigned int*) (ioaddr2+0x2d0)) = 0x1;

*(( unsigned int*) (ioaddr2+0x2d4)) = 0x1b0000;

printk("ioaddr reg 0x%x\n",*(( unsigned int*) (ioaddr2+0x2d0))); <-- shows 1 which is OK

printk("ioaddr reg 0x%x\n",*(( unsigned int*) (ioaddr2+0x2d4))); <-- shows 0 while expected 0x1b0000 !!!!!

if (!ioaddr2)

return;

iounmap(ioaddr2);

4.

I have also tried to change in kernel boot code as following. It did not help.

clkp_osc1 = clk_get(NULL,"osc1_clkin_ck");

clk_rate = clk_get_rate(clkp_osc1);

clk_set_rate(clkp_osc1, 24576000) ;

clkp_audio_pll = clk_get(NULL,"audio_dpll_clkin_ck");

ret = clk_set_parent(clkp_audio_pll, clkp_osc1); //required for mcasp2

clkp_mcasp3 = clk_get(NULL,"davinci-mcasp.3");

ret = clk_set_parent(clkp_mcasp3, clkp_audio_pll); <------------- return -22 !

5. I have also validated that the module is ON:

root@dm814x:~# devmem2 0x4818156c

/dev/mem opened.

Memory mapped at address 0x400b9000.

Read at address 0x4818156C (0x400b956c): 0x00000002

6. also tried to change the registers using devmem2 but it always read back 0 !!

oot@dm814x:~# devmem2 0x481c62d0

/dev/mem opened.

Memory mapped at address 0x40265000.

Read at address 0x481C62D0 (0x402652d0): 0x00000000

root@dm814x:~# devmem2 0x481c62d4

/dev/mem opened.

Memory mapped at address 0x40107000.

Read at address 0x481C62D4 (0x401072d4): 0x00000000

root@dm814x:~# devmem2 0x481c62d4 0xffffffff

/dev/mem opened.

Memory mapped at address 0x40203000.

Illegal data type '0'.

root@dm814x:~# devmem2 0x481c62d4 w 0xffffffff

/dev/mem opened.

Memory mapped at address 0x4008e000.

Read at address 0x481C62D4 (0x4008e2d4): 0x00000000

Write at address 0x481C62D4 (0x4008e2d4): 0xFFFFFFFF, readback 0xFFFFFFFF

root@dm814x:~# devmem2 0x481c62d4

/dev/mem opened.

Memory mapped at address 0x40133000.

Read at address 0x481C62D4 (0x401332d4): 0x00000000

root@dm814x:~#

I also don't understand why the default in code is that mcasp3 parent is xref0. I don't see "xref0" in audio pll tree.

Is there a power mode issue here ? What is wrong with the above ?

Thank you,

Ran