Hi Sir :

I work on TI AM335x IDK platform, the tools's version are as below.

CCS V6

am335x_sysbios_ind_sdk_1.1.0.8

bios_6_41_04_54

ndk_2_24_01_18

xdctools_3_30_06_67_core

I try to use GPMC to connect with FPGA and below is my setting.

HWREG(SOC_GPMC_0_REGS + GPMC_CONFIG1(csNum)) = 0x28001000;

HWREG(SOC_GPMC_0_REGS + GPMC_CONFIG2(csNum)) = 0x00050500;

HWREG(SOC_GPMC_0_REGS + GPMC_CONFIG3(csNum)) = 0x00020202;

HWREG(SOC_GPMC_0_REGS + GPMC_CONFIG4(csNum)) = 0x05000500;

HWREG(SOC_GPMC_0_REGS + GPMC_CONFIG5(csNum)) = 0x00050505;

HWREG(SOC_GPMC_0_REGS + GPMC_CONFIG6(csNum)) = 0x50000000;

HWREG(SOC_GPMC_0_REGS + GPMC_CONFIG7(csNum)) = 0xF50;

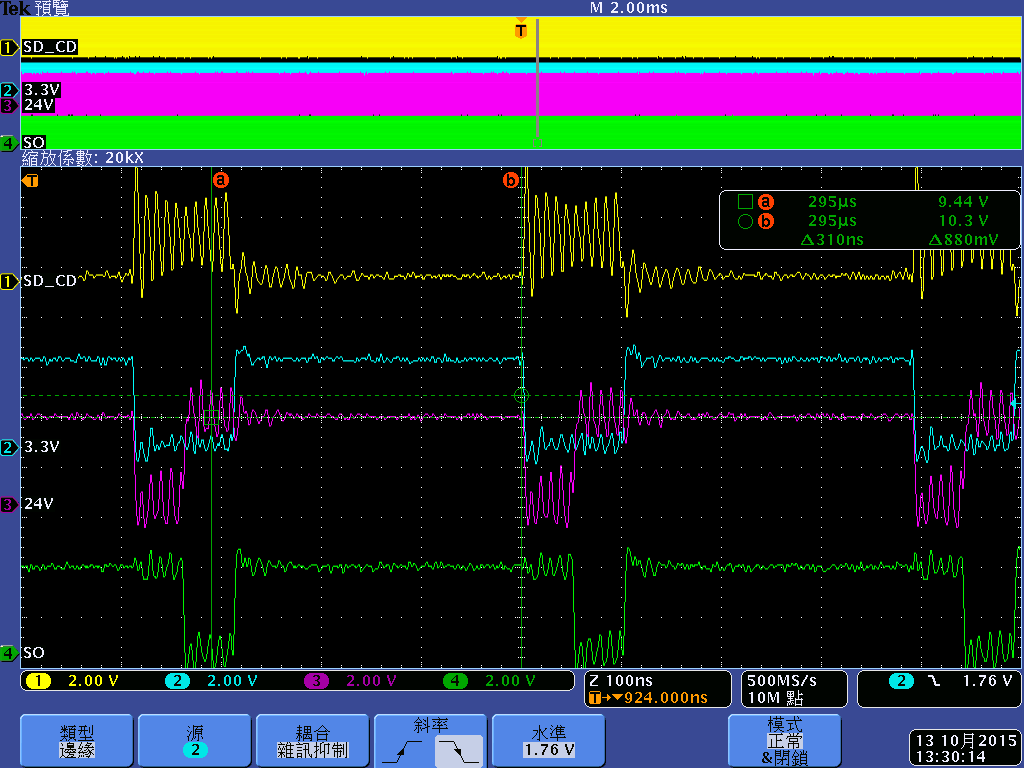

Ch1 is GPMC Clock

Ch2 is CS

Ch3 is OE

Ch4 is WE

As you can see, there is 310 ns between two success write/read.

My question is that is it possible to shorten the duration between two success write/read?

I have tried to change the value of GPMC_CONFIG6, but it seems no effect.

Could you give me some suggestion?

Best regards,

Marcus