I am using LCDK C6748 to get stereo Audio In/out (a loop or echo routine). I initialise and start the McASP module according to the technical reference manual instructions. The AXR serialiser lines work fine in polling and without BIOS.... but if I use the exact same code in Interrupt service routine, AXR in TX/RX mode is dead. The ACLK, AFS, and AHCLK are fine in either case.

When I move from polling to Interrupt based program, these are the steps I take

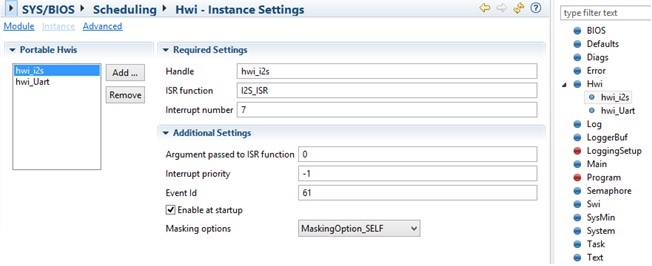

1. I define the ISR routine, reference it in HWI in app.cfg (Associate McASP Event #61 to CPU interrupt #5)

2. The corresponding bit in IER register is enabled in main.c. ( to enabled GIE and IER)

3. I also enabled mcaspRegs->XINTCTL = 0x00000020; // RDATA ready

mcaspRegs->RINTCTL = 0;

The code for ISR is transmits 0x55555555 for slot 0 and 0x7FFFFFFF for Slot 1, since this is I2S serial line. (please ignore the RX buffer for now, i can't even get TX to transmit any value in interrupt mode)

void I2S_ISR(void) {

Log_info0("Entered McASP isr");

if (mcaspRegs->XSTAT & 0x00000020) // If Tx data ready flag is up

{

if (mcaspRegs->XSTAT & 0x00000040) // start of frame

{

mcaspRegs->XBUF7 = 0x55555555;

mcaspRegs->XSTAT = 0x00000040; // clear the start of frame flag

} else if (mcaspRegs->XSTAT & 0x00000010)// if it is last slot of frame

{

mcaspRegs->XBUF7 = 0x7FFFFFFF;

mcaspRegs->XSTAT = 0x00000010; // clear last slot flag

}

mcaspRegs->XSTAT |= 0x00000020; // clear XDATA flag

}

}

Any help please?