My goal is to achieve Stereo Audio echo. Before echo, I want to see if AXR7 pin (a serialiser used as a TX) even transmits or not..

I followed instructions for McASP initialisation and starting up module from C6000 peripheral guide.pdf. It works for polling but not for Interrupt. Here is the problem:

When I use polling, the AXR7 line on LCDKc6748 ( pin #28 on J15 pin header) transmits data on each slot (slot 0 &1 for 2-slot TDM, I2S protocol). But when I start BIOS and use the exact same code for Interrupt based system, TX line is dead. Underrun and XERR occur.

The initialisation and startup of polling and interrupt are exactly the same. The only difference is that in polling, I put the polling code inside a while(1) loop before BIOS_start() command. For McASP, I remove the while{1} loop and put the exact same code into I2S_ISR() which is called upon Hwi.

My code that works on polling is as follows

while (1) // loop forever

{

if (mcaspRegs->XSTAT & 0x00000020) // If Tx data ready flag is up

{

if (mcaspRegs->XSTAT & 0x00000040) // start of frame

{

mcaspRegs->XBUF7 = 0x55555555;

mcaspRegs->XSTAT = 0x00000040; // clear the start of frame flag

} else if (mcaspRegs->XSTAT & 0x00000010)// if it is last slot of frame

{

mcaspRegs->XBUF7 = 0x7FFFFFFF;

mcaspRegs->XSTAT = 0x00000010; // clear last slot flag

}

mcaspRegs->XSTAT |= 0x00000020; // clear XDATA flag

}

}

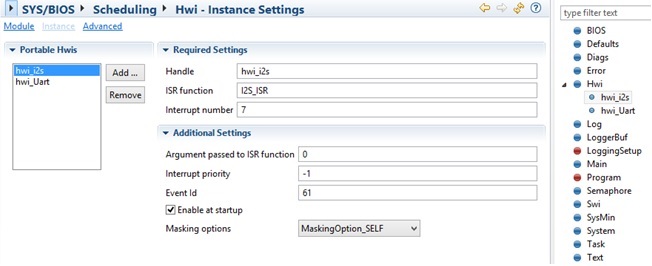

Then I copy the same code into I2S_ISR() and in app.cfg, following settings on app.cfg

| UART_ISR | Event # 69 | CPU interrupt #5 |

| I2S_ISR | Event #61 | CPU interrupt #7 |

Also in McASP initialisation, I allow TX interrupt

mcaspRegs->XINTCTL = 0x00000020;

Even if I interchange the CPU interrupt so that McASP has a higher priority than UART and is uninterrupted (BTW UART for me works fine)..... still nothing on the TX line!!! the XBUFn shows the value that I have written on it in my code. Please see my project attached. It is located in C:\ti\WorkspaceI2S Master.rar