Hi,

I have the following settings and I would like to understand how to boot directly from NOR

- I access an external NOR flash (8MB) using EMIFA and GPIO's

- My code exceeds 32KB which is the max boot image seen by bootloader in the case of CS2 having 15 address lines EMA_BA[1:0] and EMA_A[12:0]

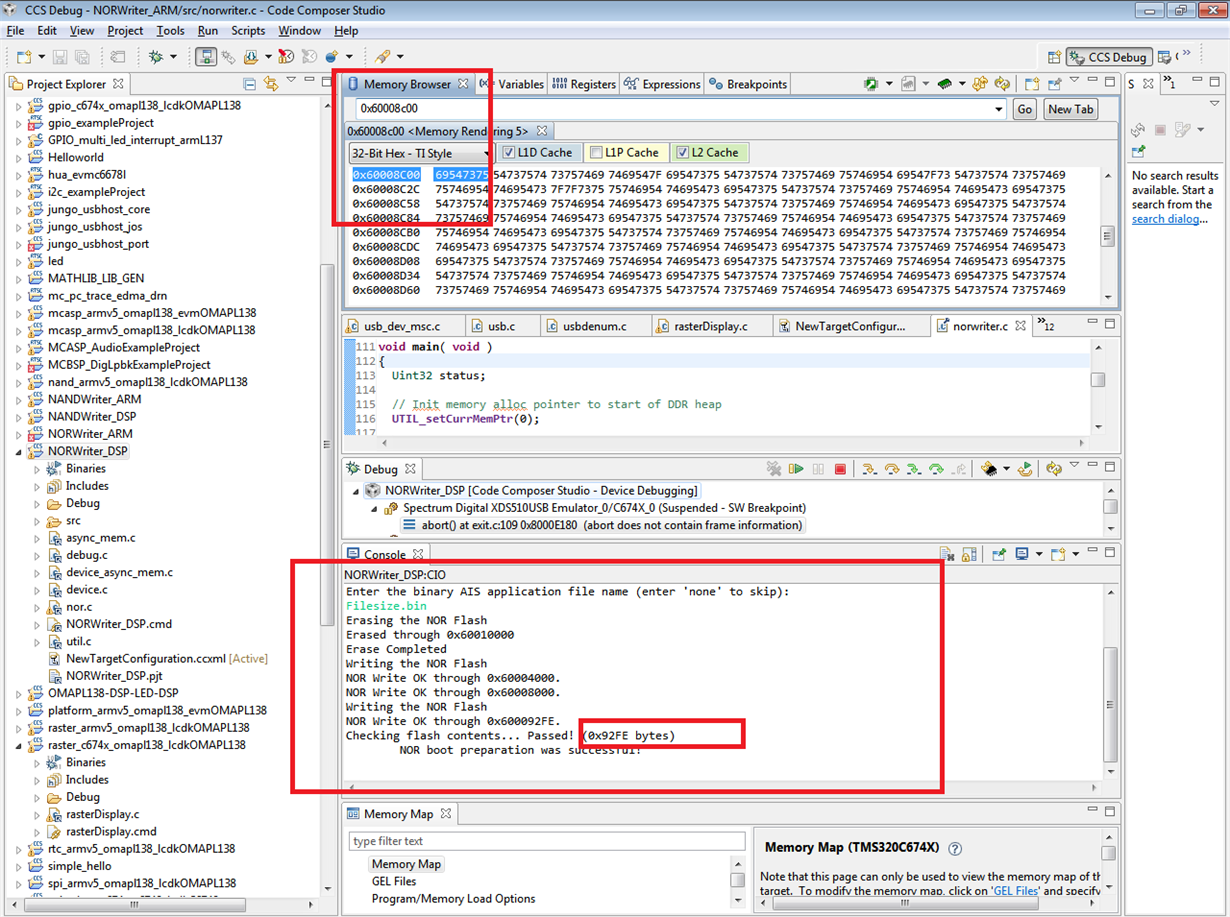

- I already used AIS and NORWRITER to flash a small code and it works ok

My question is :

I want to use the method NOR direct described by bootloader document but I don't know how.

I tried to follow the Talk:Secondary Bootloaders on OMAP-L1x but the .text section is too small for my case.

how can I place all my code in this section knowing that only 32 KB is possible. should I extend the section PROG_NOR to include all the space available in my NOR flash space, and how and where exactly GPIO's would be set to allow CPU reading/writing from/to the upper address lines of the NOR.

MEMORY {

CFG_NOR: o = 0x60000000 l = 0x00000020 PROG_NOR: o = 0x60000020 l = 0x00003FE0 PROG_L2RAM: o = 0x11800000 l = 0x00002000

}

SECTIONS {

.entryPoint > PROG_NOR .text > PROG_NOR .const > PROG_NOR .switch > PROG_NOR .cinit > PROG_NOR .far > PROG_L2RAM .data > PROG_L2RAM .bss > PROG_L2RAM .cio > PROG_L2RAM .stack > PROG_L2RAM .sysmem > PROG_L2RAM .nor_cfg_word > CFG_NOR

}

Thank you for your support