I have problem with init ports into SGMII in Ethernet Gigabit SubSystem. I use TMS320C6678 1000 MHz device with

the Alaska Ultra 88E1111 Gigabit Ethernet Transceiver. It's customer board, not EVM. My text for init:

/* init psc */

static void _init_psc()

{

CSL_PSC_enablePowerDomain(CSL_PSC_PD_PASS);

CSL_PSC_setModuleNextState(CSL_PSC_LPSC_PKTPROC, PSC_MODSTATE_ENABLE);

CSL_PSC_setModuleNextState(CSL_PSC_LPSC_CPGMAC, PSC_MODSTATE_ENABLE);

CSL_PSC_startStateTransition(CSL_PSC_PD_PASS);

while(!CSL_PSC_isStateTransitionDone(CSL_PSC_PD_PASS));

}

/* init pll */

static void _init_pll()

{

u32 pllst;

union _cfgpll_t

{

u16 data;

struct

{

u16 en : 1;

u16 mpy : 7;

u16 endiv : 1;

u16 vrange : 1;

u16 sleep : 1;

u16 loop_bw : 2;

u16 bypass : 2;

u16 std : 1;

};

};

union _cfgrx_t

{

u32 data;

struct

{

u32 en : 1;

u32 busw : 3;

u32 rate : 2;

u32 invpair : 1;

u32 term : 3;

u32 align : 2;

u32 los : 3;

u32 cdr : 3;

u32 eq : 4;

u32 enoc : 1;

u32 lo : 2;

u32 : 7;

};

};

union _cfgtx_t

{

u32 data;

struct

{

u32 en : 1;

u32 busw : 3;

u32 rate : 2;

u32 invpair : 1;

u32 cm : 1;

u32 swing : 4;

u32 demph : 4;

u32 mysnc : 1;

u32 enidl : 1;

u32 rdtct : 2;

u32 lo : 2;

u32 : 10;

};

};

/* pll config */

_cfgpll_t pll = { 0 };

pll.en = 1;

pll.vrange = 1;

pll.mpy = 20; /* 5x == 7'b0010100 */

/* RX config */

_cfgrx_t rx = { 0 };

rx.en = 1;

rx.rate = 2;

rx.term = 4;

rx.align = 1;

rx.eq = 12;

rx.enoc = 1;

/* TX config */

_cfgtx_t tx = { 0 };

tx.en = 1;

tx.rate = 2;

tx.cm = 1;

tx.swing = 8;

tx.mysnc = 1;

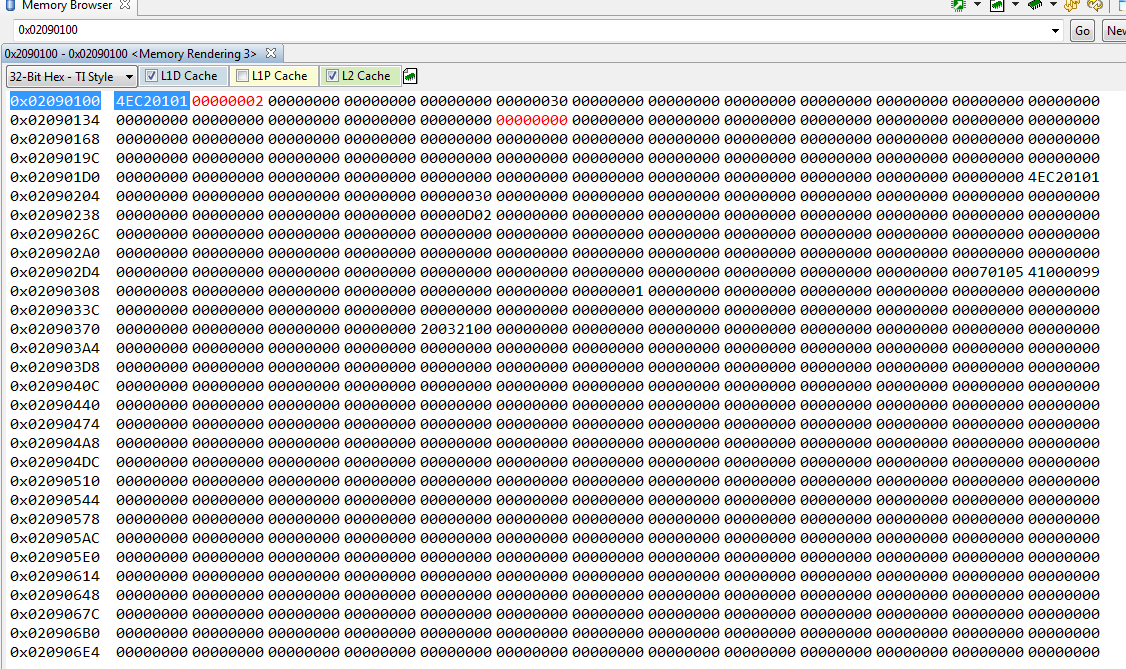

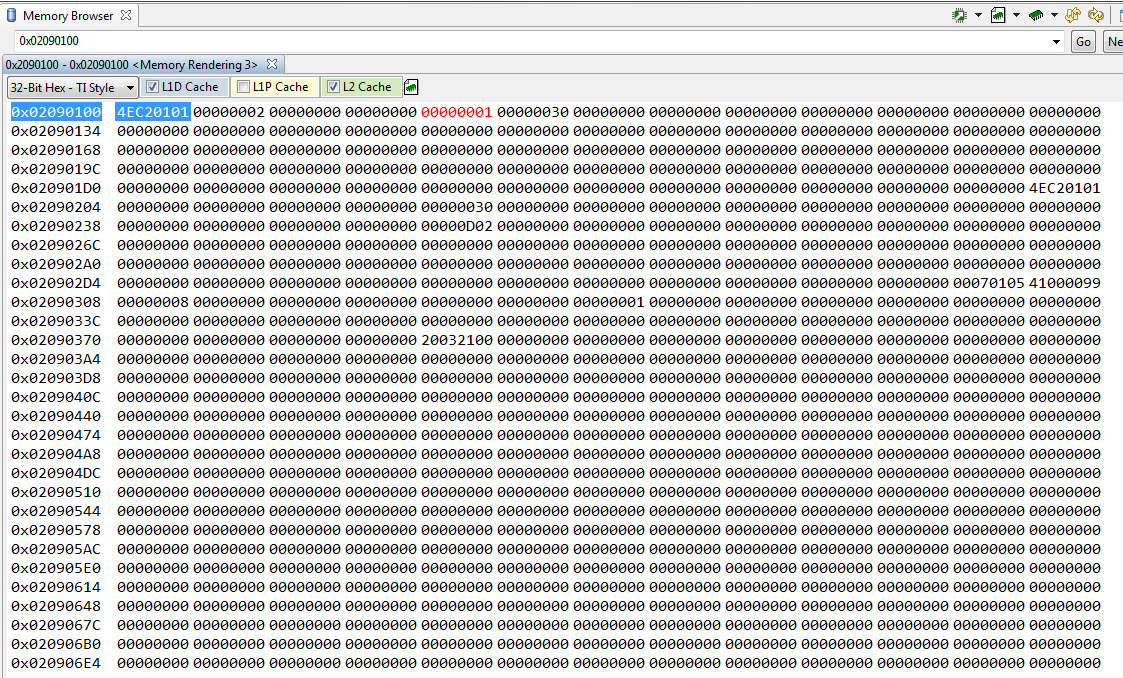

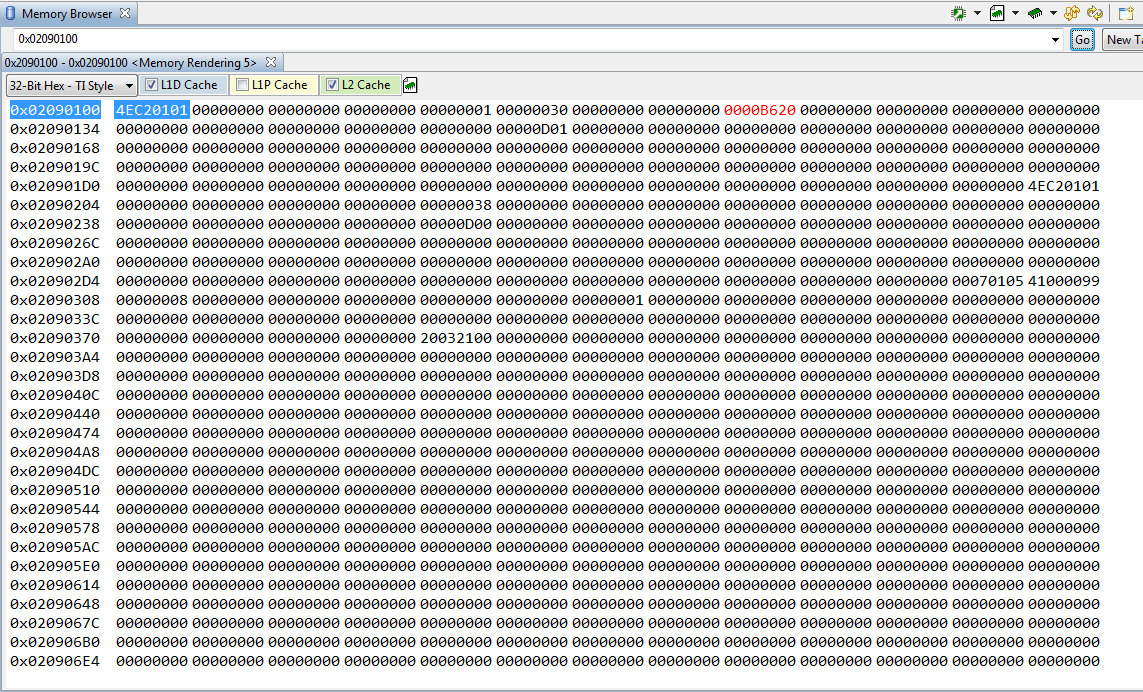

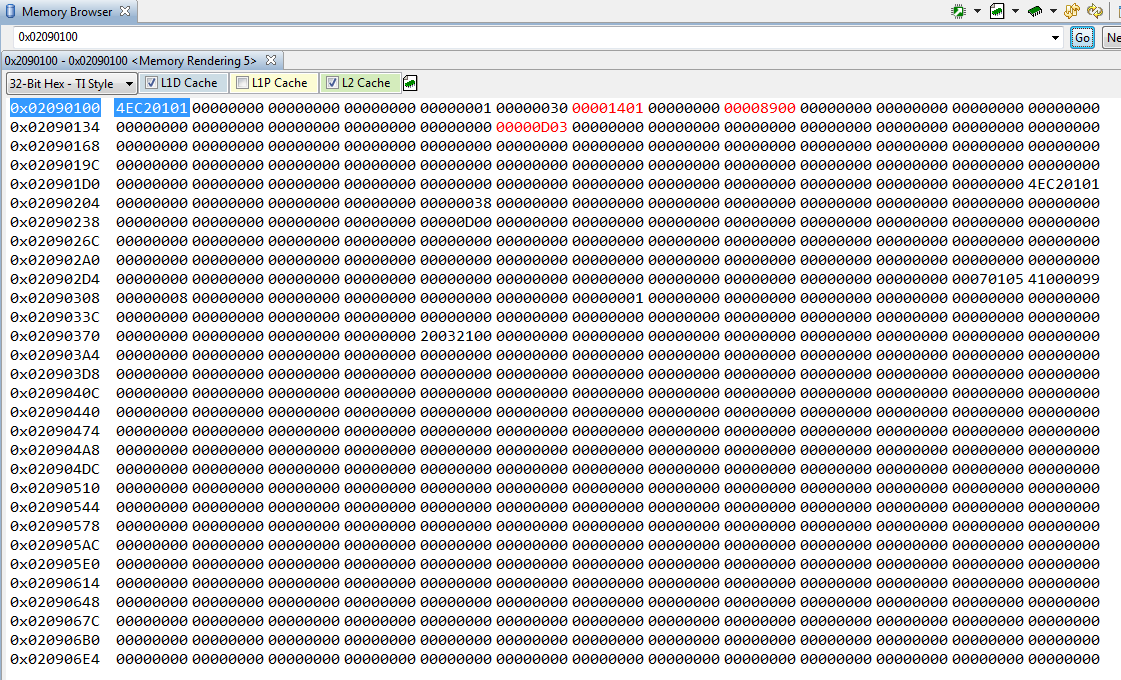

/* Unlock the chip configuration registers to allow SGMII SERDES registers to

* be written */

CSL_BootCfgUnlockKicker();

CSL_BootCfgSetSGMIIConfigPLL(pll.data);

s32 cnt = -1;

do

{

cnt++;

CSL_BootCfgGetSGMIISERDESStatus(&pllst);

}

while((pllst & 0x00000001) == 0);

CSL_BootCfgSetSGMIIRxConfig(0, rx.data);

CSL_BootCfgSetSGMIITxConfig(0, tx.data);

CSL_BootCfgSetSGMIIRxConfig(1, rx.data);

CSL_BootCfgSetSGMIITxConfig(1, tx.data);

CSL_BootCfgLockKicker();

}

/* init port */

static void _init_port(u32 id)

{

CSL_SGMII_ADVABILITY cfg = { 0 };

CSL_SGMII_STATUS status = { 0 };

/* reset SGMII */

CSL_SGMII_doSoftReset(id);

while(CSL_SGMII_getSoftResetStatus(id) != 0);

/* Hold the port in soft reset and set up

* the SGMII control register:

* (1) Enable Master Mode (default)

* (2) Enable Auto-negotiation

*/

CSL_SGMII_startRxTxSoftReset(id);

CSL_SGMII_disableMasterMode(id);

/* Setup the Advertised Ability register for this port:

* (1) Enable Full duplex mode

* (2) Enable Auto Negotiation

*/

cfg.linkSpeed = CSL_SGMII_100_MBPS;

cfg.duplexMode = CSL_SGMII_FULL_DUPLEX;

CSL_SGMII_setAdvAbility(id, &cfg);

CSL_SGMII_enableAutoNegotiation(id);

CSL_SGMII_endRxTxSoftReset(id);

/* wait for SGMII link */

CSL_SGMII_restartAutoNegotiation(id);

do

{

CSL_SGMII_getStatus(id, &status);

}

while(status.bIsLinkUp != 1);

/* I have error */

. . . .

}

I take boot parameters from TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor

2.5.4 PLL boot Configuration Settings - page 41.

Where I make eror?

Best regards,

Oleg