Hello TI' teams,

I found little difference between 2 documents that describes C67x megamodule on DM8148 processor.

tms320dm8148.pdf describe DSP and megamodule subsystem as:

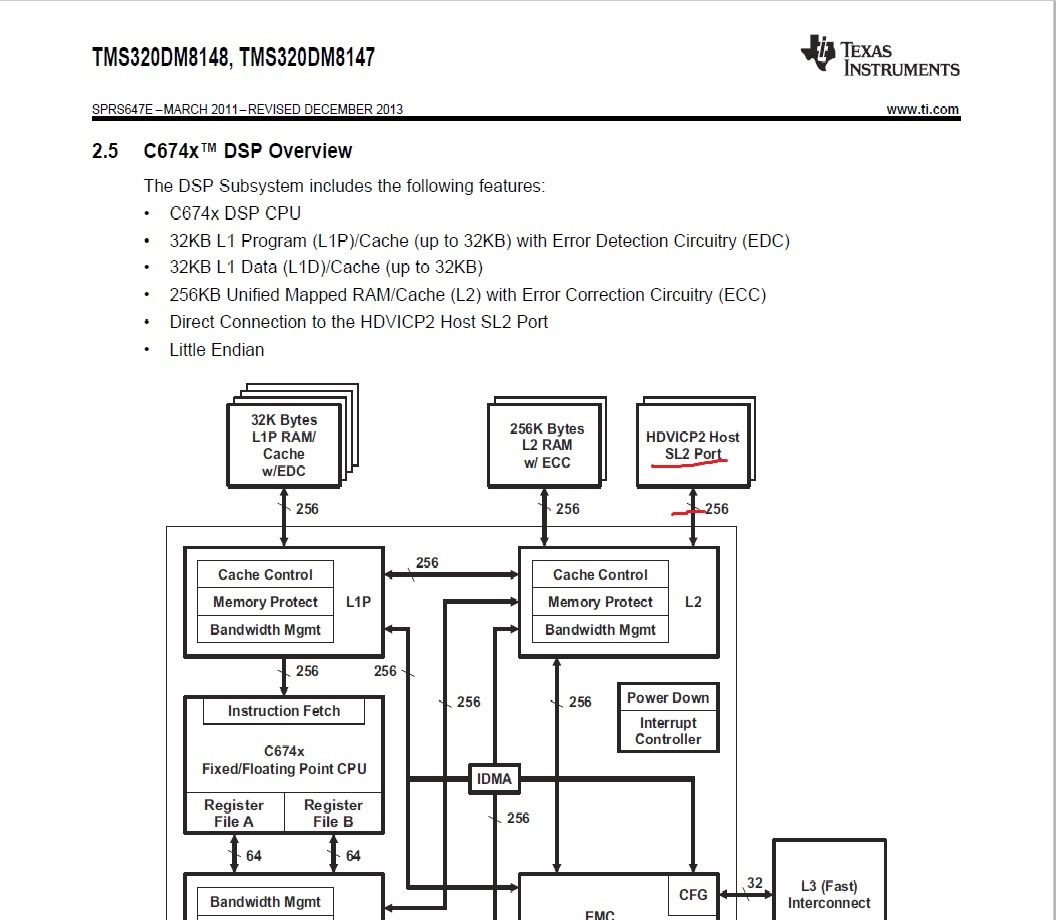

The DSP Subsystem includes the following features:

• C674x DSP CPU

• 32KB L1 Program (L1P)/Cache (up to 32KB) with Error Detection Circuitry (EDC)

• 32KB L1 Data (L1D)/Cache (up to 32KB)

• 256KB Unified Mapped RAM/Cache (L2) with Error Correction Circuitry (ECC)

• Direct Connection to the HDVICP2 Host SL2 Port

• Little Endian

When DM8148 TRM (sprugz8e.pdf and sprufk5a.pdf) :

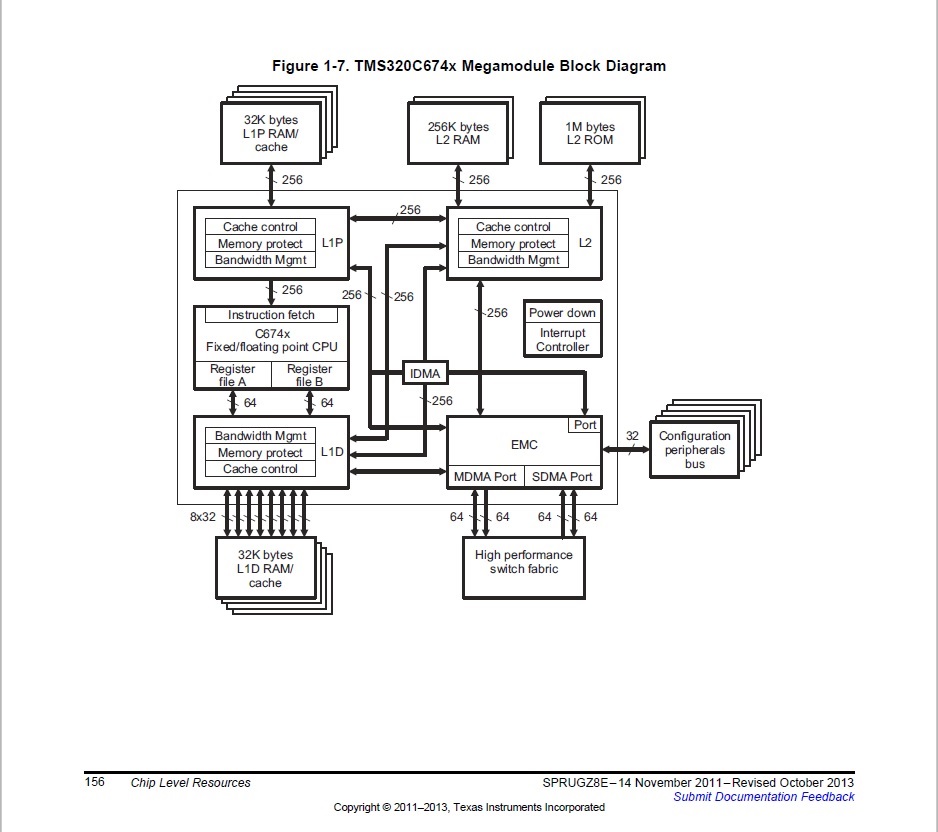

The C674x megamodule (Figure 1-7) consists of the following components:

• TMS320C674x CPU

• Internal memory controllers:

– Level 1 program memory controller (PMC)

– Level 1 data memory controller (DMC)

– Level 2 unified memory controller (UMC)

– Extended memory controller (EMC)

– Internal direct memory access (IDMA) controller

• Internal peripherals:

– Interrupt controller (INTC)

– Power-down controller (PDC)

– Bandwidth manager (BWM)

• Advanced event triggering (AET)...

And no any word about connect between c674x/L2 to HDVICP2.

C674x megamodule block diagram different too in TRM and in tms320DM8148.pdf - plz see attcahed images.

The difference: 256 bits bus "Direct Connection to the HDVICP2 Host SL2 Port".

Please let me known, what diagram is wrong?