Hi all,

we are developing a product basing on Keystone2 TCI6638k2k. We have 2GB connected to DDR3A and 2GB connected to DDR3B.

From my test it seems that DSPs are able to access DDR3A instead of DDR3B when accessing an address greater than 0x8000_0000. We are setting DDR3A_REMAP_EN=1 and I double checked it by reading the corresponding register. So, basing on my understanding of the datasheet, I should see the memory this way:

|

Address

|

ARM (DDR3A_REMAP_EN=1)

|

DSPs

|

|

0x00_6000_0000

|

DDR3B

|

DDR3B (alias of 0x00_8000_0000)

|

|

0x00_8000_0000

|

DDR3A (alias of 0x08_0000_0000)

|

DDR3B

|

|

0x08_0000_0000

|

DDR3A

|

DDR3A

|

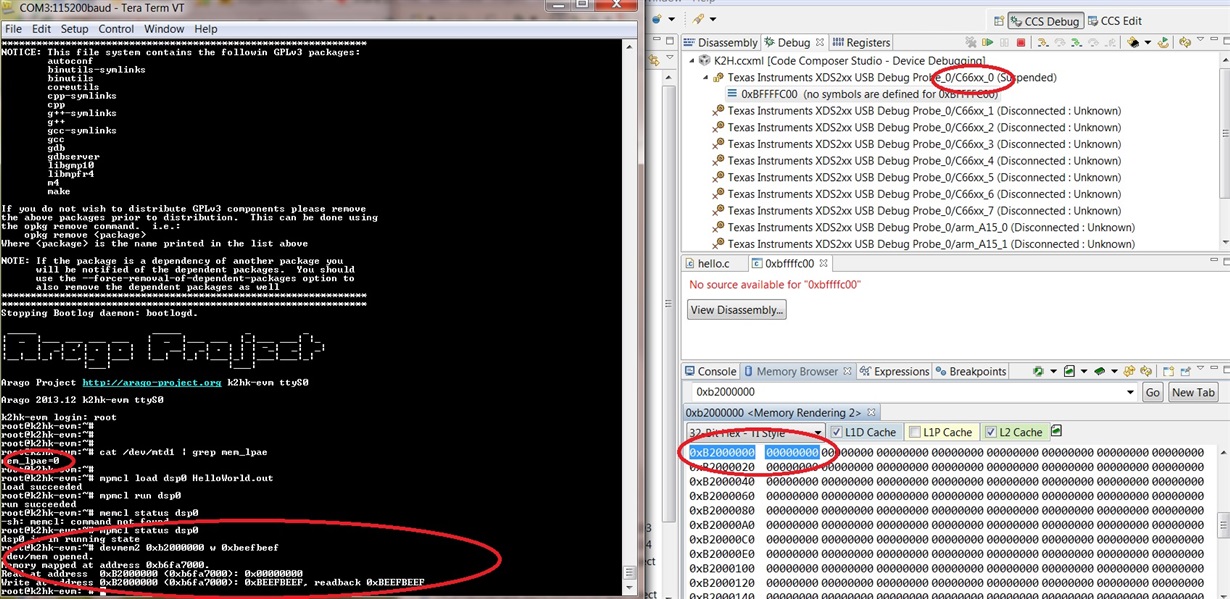

As mentioned, when DSPs access an address in the range 0x8000_0000 - 0xffff_ffff they are able to see data written from the ARM side, which is DDR3A. For example, I write some words at 0xb200_0000 and DSP2 reads such words when accessing the same address (I am loading the DSP code by using the mpmcl command). Basing on my understanding, ARM and DSPs should work on different physical memories and they shouldn't see each others.

Is there any obvious reason that leads this behavior?

P.S. I am pretty sure that ARM is seeing the correct DDR3A memory. One thing that should confirm this is that U-boot actually puts the Linux code into the aliased memory at 0x8000_0000, Linux starts in PAE mode and it runs at physical address 0x08_0000_0000 without problems.

Thanks a lot for your support.

N.