DDR routing question

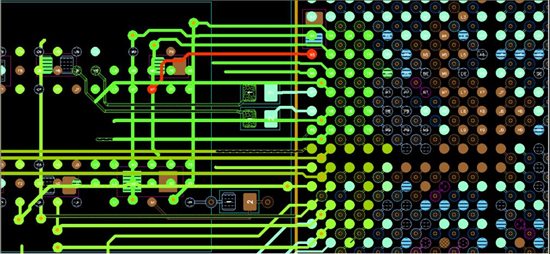

My question has to do with determining the 'Target' length of my routes for the net class that is referred to in Table 6-35 on page 123 of OMAP-L138 Low-Power Applications Processor (SPRS586A–JUNE 2009–REVISED AUGUST 2009). I need to know how to correctly interpret item 4 for 'CACLM' which refers to the 'longest Manhattan distance of the CK and ADDR_CTRL net classes'.

On my board the longest route in this net class is less than the 'longest Manhattan distance of the CK and ADDR_CTRL net class' (which would be measured between the pair of pins farthest from each other in this 'net class' that run between the 2 devices).

Can this shorter length be used or do I need to add extra length to this route (and all the others) to match the actual Manhattan distance I measured from pin to pin?

I would prefer to not add extra length as the routing is already congested. Thanks for any assistance.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.