while trying to boot AM3352BZCEA60 DDR3 IS43TR16256AL-15HBL one our custom board. we are facing issue in bootup

we used

u-boot from arago repository

arago-project.org/.../

And kernel from that is latest supplied by through beaglebone Angstrom website. kernel 4.1.4

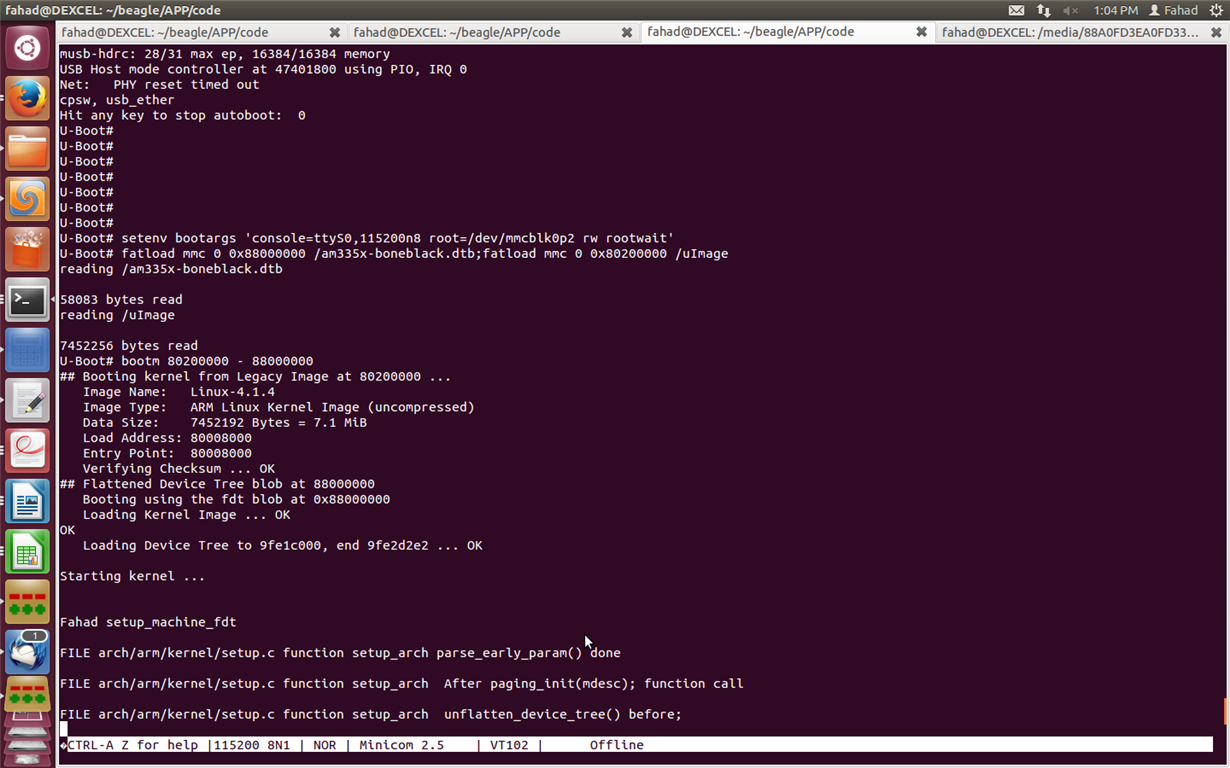

U-Boot# bootm 80200000 - 88000000

## Booting kernel from Legacy Image at 80200000 ...

Image Name: Linux-4.1.4

Image Type: ARM Linux Kernel Image (uncompressed)

Data Size: 7452192 Bytes = 7.1 MiB

Load Address: 80008000

Entry Point: 80008000

Verifying Checksum ... OK

## Flattened Device Tree blob at 88000000

Booting using the fdt blob at 0x88000000

Loading Kernel Image ... OK

OK

Loading Device Tree to 9fe1c000, end 9fe2d2e2 ... OK

Starting kernel ...

FILE arch/arm/kernel/setup.c function setup_arch parse_early_param() done

FILE arch/arm/kernel/setup.c function setup_arch After paging_init(mdesc); function call

FILE arch/arm/kernel/setup.c function setup_arch unflatten_device_tree() before;

No response from device after this print

We have modified slightly in u-boot according to our DDR3L values

arago-u-boot$ vim arch/arm/include/asm/arch-am33xx/ddr_defs.h settings below

/* Micron MT41J128M16JT-125 */

#define DDR3_EMIF_READ_LATENCY 0x100006 /* Enable Dynamic Power Down */

#define DDR3_EMIF_TIM1 0x0888A39B

#define DDR3_EMIF_TIM2 0x26337FDA

#define DDR3_EMIF_TIM3 0x501F830F

#define DDR3_EMIF_SDCFG 0x61C04B32

#define DDR3_EMIF_SDREF 0x0000093B

#define DDR3_ZQ_CFG 0x50074BE4

#define DDR3_DLL_LOCK_DIFF 0x1

#define DDR3_RATIO 0x40

#define DDR3_INVERT_CLKOUT 0x1

#define DDR3_RD_DQS 0x3B

#define DDR3_WR_DQS 0x85

#define DDR3_PHY_WR_DATA 0xC1

#define DDR3_PHY_FIFO_WE 0x100

#define DDR3_IOCTRL_VALUE 0x18B

/* Micron ???? on 1.5 and later EVMs */

#define DDR3_EMIF_TIM2_EVM 0x26517FDA

#define DDR3_EMIF_TIM3_EVM 0x501F851F

#define DDR3_RD_DQS_EVM 0x3A

#define DDR3_WR_DQS_EVM 0x0CD

#define DDR3_PHY_FIFO_WE_EVM 0x10B

#define DDR3_PHY_WR_DATA_EVM 0x106

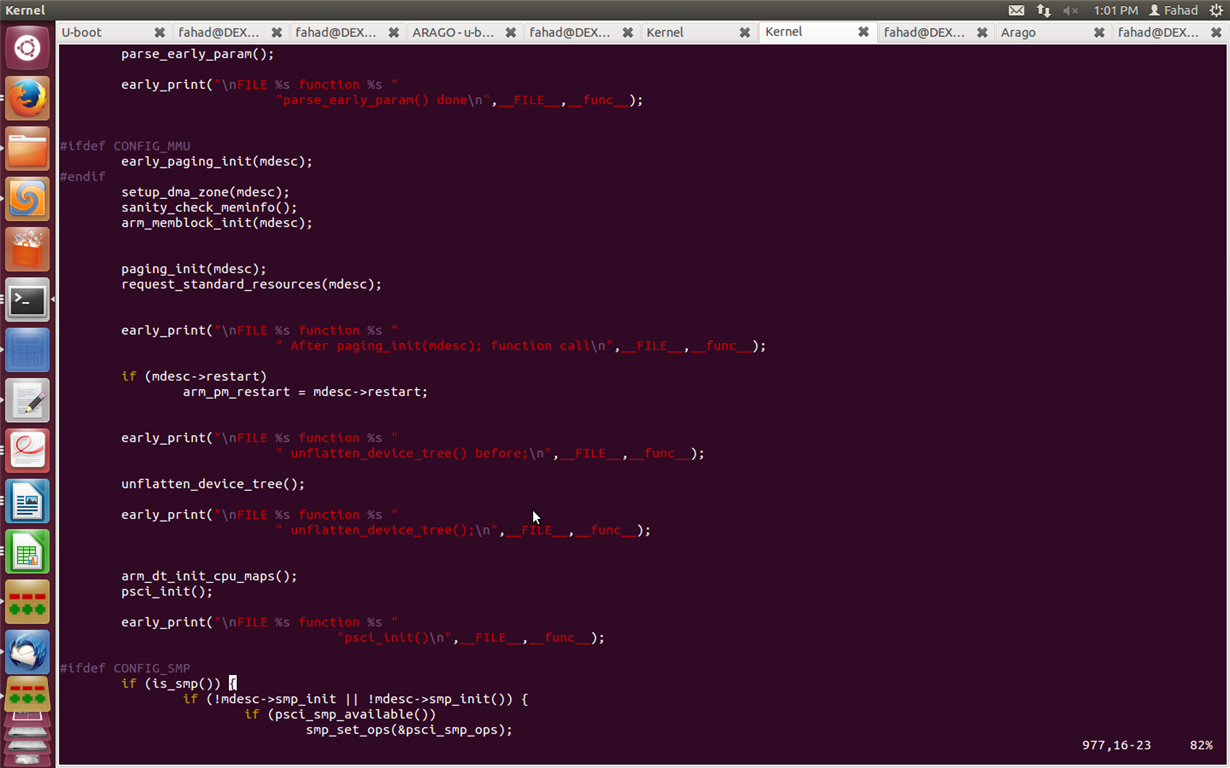

We can see u-boot boots up after loading the kernel and after paging initialization the kernel crashed in unflatten_device_tree() before; function