My cusotomer is designing AM437x USB Host + USB Hub system from following informations.

- Wiki

processors.wiki.ti.com/.../AM437x_Schematic_Checklist

- e2e USB interface

e2e.ti.com/.../804511

- e2e USB host without VBUS and DRVVBUS

e2e.ti.com/.../239776

- e2e USB Host with USBHUB operation

e2e.ti.com/.../1281293

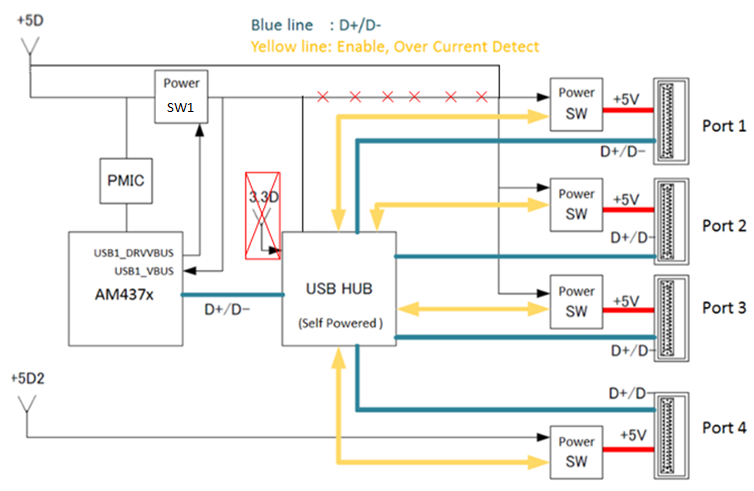

The block block diagram is like follows.

AM437x.USB1 is USB Host and AM437x.USB0 is used for USB Device although USB0 is not on block diagram.

+5D is source power for VBUS of Port1,2,3.

+5D2 is source power for VBUS of Port4

+5D and +5D2 have no relation each other.

AM437x.USB1.DRVVBUS and AM437x.USB1.VBUS can manage +5D but can not manage +5D2.

Is this design OK ? or what should be applied for good design ?

Regards,

Takeshi Matsuzaki