Hi TI Experts,

Please let me confirm the usage of SAR ADC on C5535.

Would you please teach me the registers to use the GPAIN0 pin?

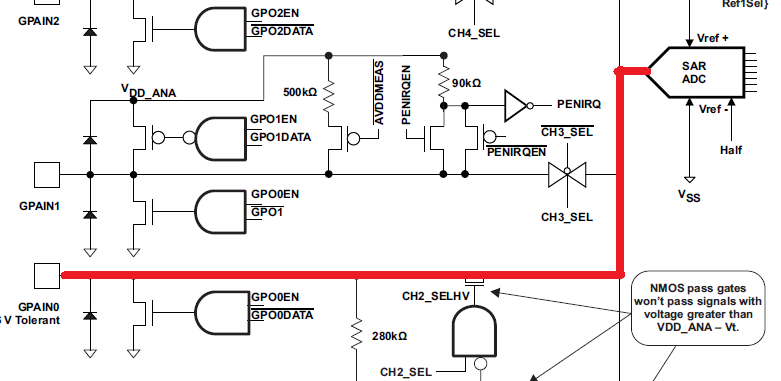

My customer would like to use the following path. So they would like to know the register settings to use this path.

---------Edit --------

I confirmed the customer's settings for SAR resisters.

SARCTRL: 0xA000

SARCLKCTRL:0x0031

SYSCLK: 98MHz

SARPINCTRL:0x3102

SARGPOCTRL:0x0000

If you find any problem for this values, please let me know.

If you have any questions, please let me know.

Best regards.

Kaka