Нi All!

This topic is not actually a problem rather a solution for any one who is facing the same. Solution to the problem with bringing up SGMII link. We struggled with it for 3+ months, but finally the resolution was found.

The problem was that we were unable to bring up SGMII link with Marvel 88e1111. It is briefly described in this topic of my colleague: https://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/t/473291

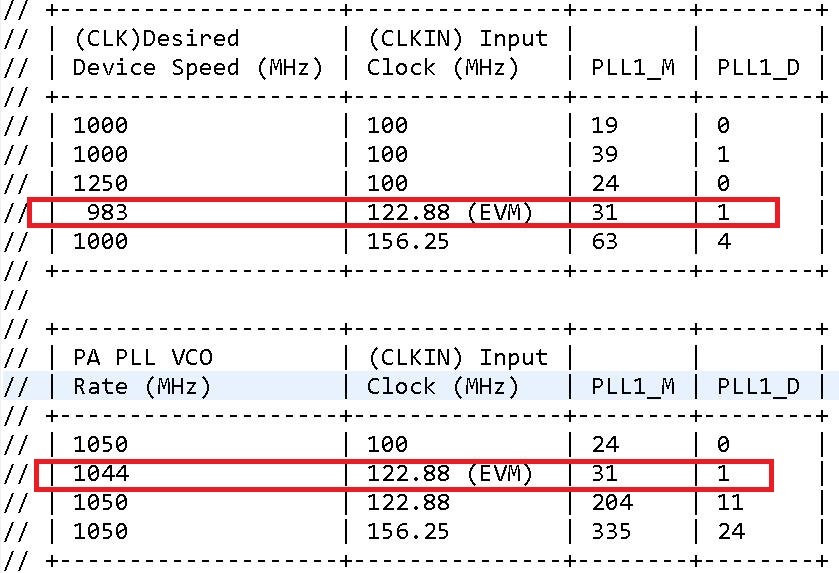

We had CORECLK/PASSCLK of 122.88 MHz. Don't ask me why (because it is recommended in the manuals?). PASS PLL was using CORECLK and set up according to Table 2-24 of TMS320C6678 manual (SPRS691E) PLLM=204, PLLD=11. SerDes and SGMII were also set up according to corresponding data manuals, but autonegotiation and link with PHY always failed. SGMII loopback and SerDes loopback worked just fine.

After numerous changes of registers values, digging in specifications, changing PHY clock sources and fighting with oscilloscope at 1.25 GHz we were almost defeated with this and even consider changing the layout of our PCB.

But then came salvation. And it was very simple: change CORECLK frequency to 100 MHz and get exactly 350 MHz from PASS PLL. The documentation is quite obscure in the case of PASS and SGMII interoperation. Moreover it does not state that SGMII/SerDes availability is somehow dependent on PASS input frequency.

After we moved to 100 MHz (as in dev board) everything just works as expected and PHY started to joyfully blink with its leds.

Regards,

Yurii