Hi Sir

I have two questions

1.There are 4 combination for DDRSLRATE[1:0],(fastest,fast,low,lowest),i want to know How many differences in memory actually read and write speed with different parameters(fastest,fast,low,lowest).

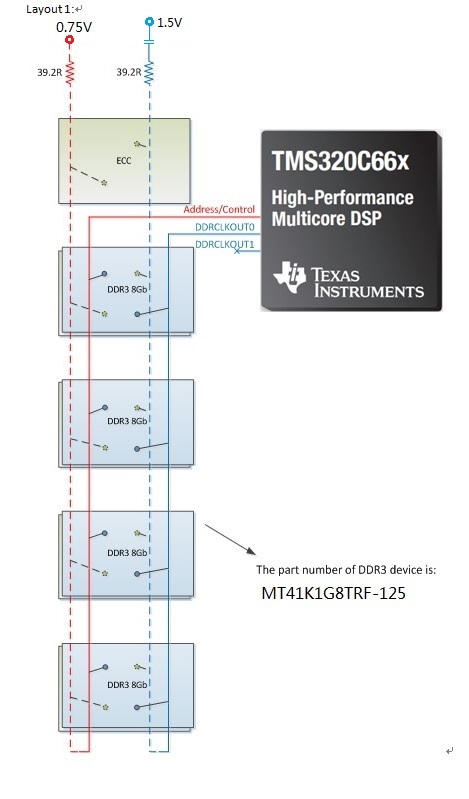

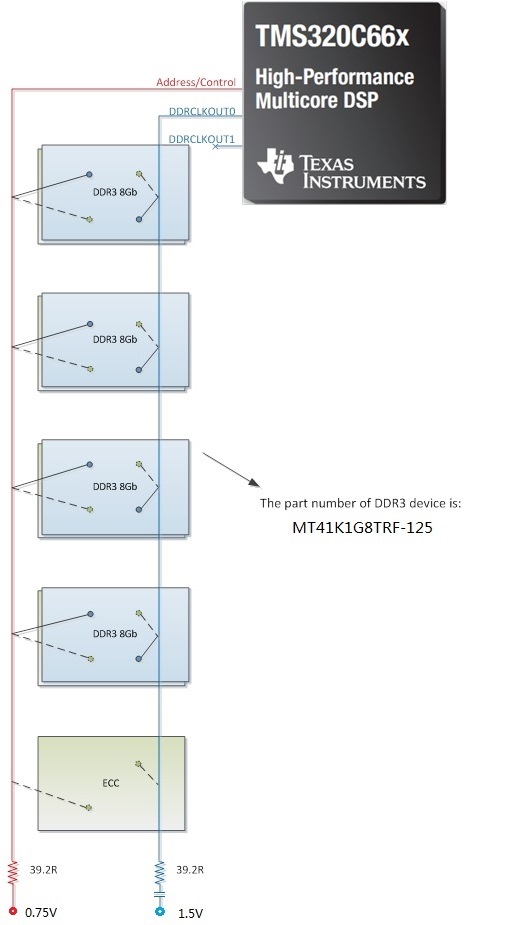

2.we use eight pcs twin-die memory components(MT41K1G8TRF-125) for C6678,five on top(ECC)on bot for PCB layout,please help to recommed the routing trace for us,Layout1 and Layout2 which is better?another question,DDRCLKOUT1 can be disconnected?thanks!