I have some problems with I2C0 on the c6713b.

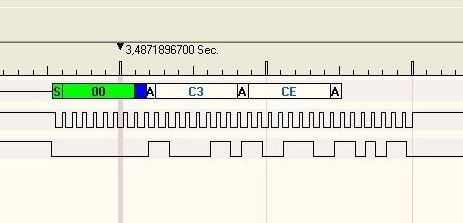

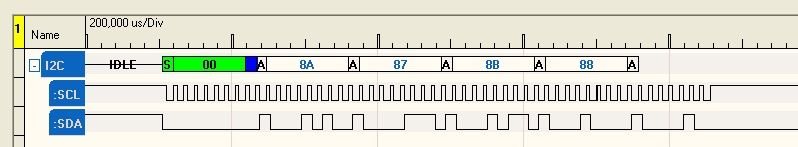

Sometimes the Bus is hanging and SDA ist Low until I toggle the SCL Line manually. Now I am trying to do this as described in the I2C Tips but it doesn't seem to work.

http://processors.wiki.ti.com/index.php/I2C_Tips

Option 2: Many devices don't mux SCL/SDA with GPIO since the I2C I/O cells are often special open drain cells. A workaround has been reported to work even on these devices. By configuring the I2C for "free data format" and then reading a byte the I2C will immediately start sending clocks to input data (rather than trying to send an address). This can be used to free up the bus.

Does anyone know how to send clocks on SCL even if SDA is held low?!

thx fabi