Hi Sir

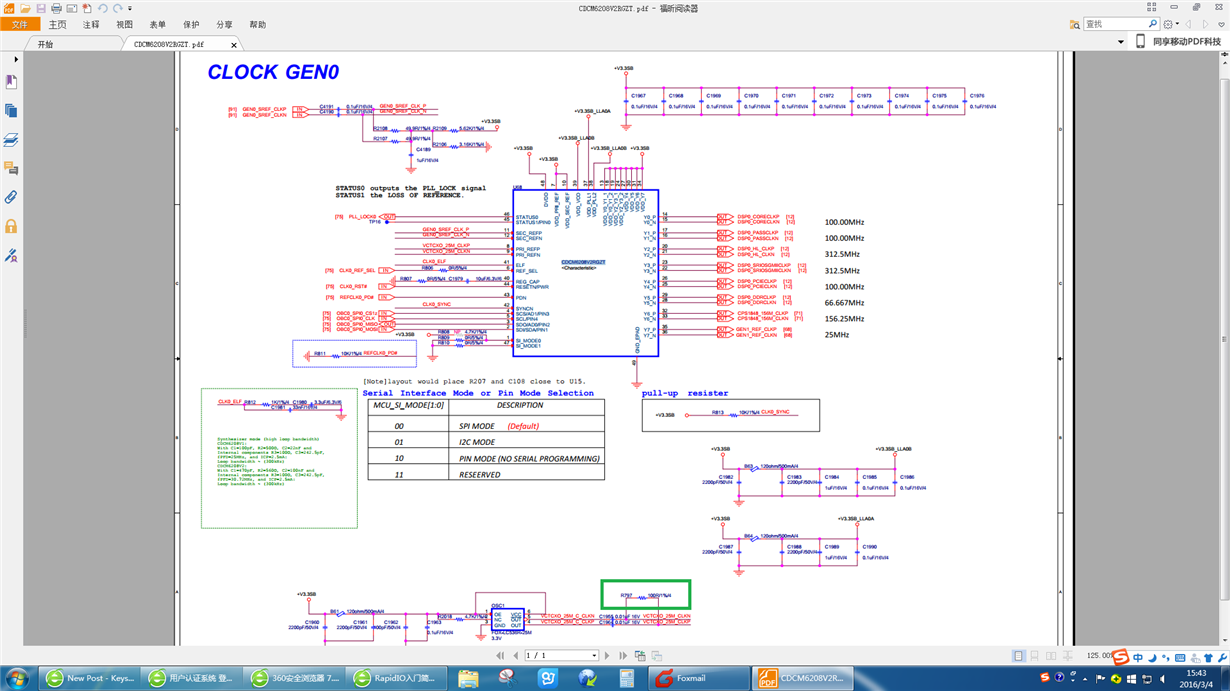

I have two question for CDCM6208V2RGZT for C6678:

1.I want to CDCM6208V2RGZT can be used in C6678?

2.Our project has a strange phenomenon, our project has four DSP(DSP0,DSP1,DSP2,DSP3),hyperlink connection Between DSP0,DSP1,another Between DSP0,DSP1, when R797 is on board for OSC1,then memory testing is stable ,but hyperlink testing is not stable between DSP0 and DSP1;

when R797 is NC,hyperlink is stable(speed 10Gpbs),but memory is not stable,Now I don't know how to debug it,please help,thanks very much.