Hi Rahul,

(Rahul knows best about my project situation)

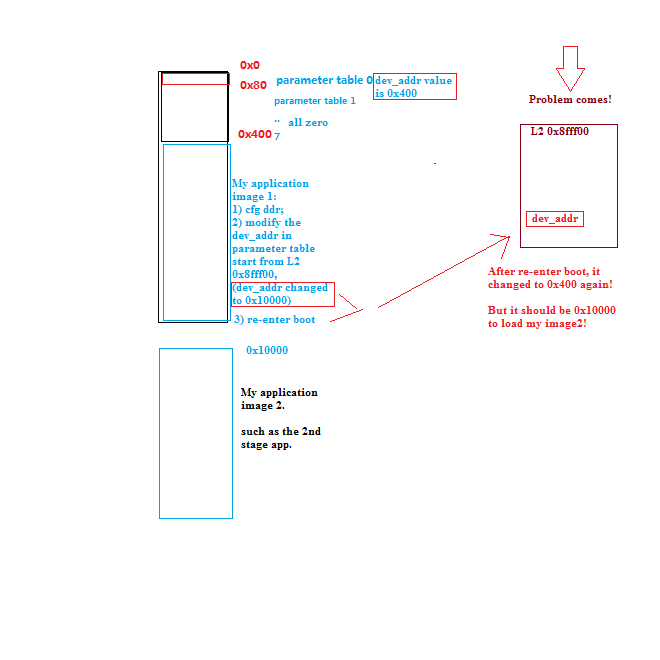

Background is here, 6638 DSP SPI boot.

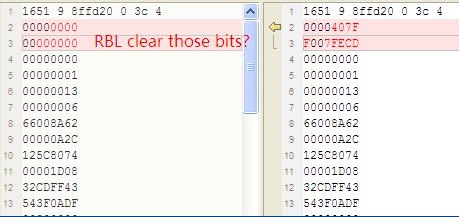

I am afraid it does not work when I put a DATA_SECTION for ddrConfigTable same as I did on 6670!

1) .gel file is verified with emulator, data/ addrss bus walking test is OK, all space addres read and write is ok when use emulator.

2)All the registers in .gel file have corresponding values in the ddrConfiTable ;

3) In 6670, I remembered when use this DATA_SECTION to config the DDR, most DDR space can be accessed and the only a small amoun of space are not normal. BUT, in 6638, I can not even access any ONE address. In my application, I juse write One address and read it back, and Flash the LED to indicate the success, but failed.

Of course , the data/address bus walking test and address filling test was also failed.

Q1,Please please confirm is it the same usage to use a DATA_SECTION to config the ddr during boot? Is there is a configuration table for 6638 SPI boot now? I know it is not available in 6670.

Q2.Please please confirm the ddrConfigTable structure, you said there is a lierature issure, please double check and send me the structure in ROM source code, only the ROM source code is reliable! (please double check the source code, do not beleive any docs,you have seen that I have discovered so many document issues now) (I was told the 6638 ROM source code can not opened, but you can copy the ddrConfigurationTable part and the other SPI boot related part to me, not the whole ROM code.)

Please please confirm!

Please confirm!

Please!

Thanks!

Regards,

Frank