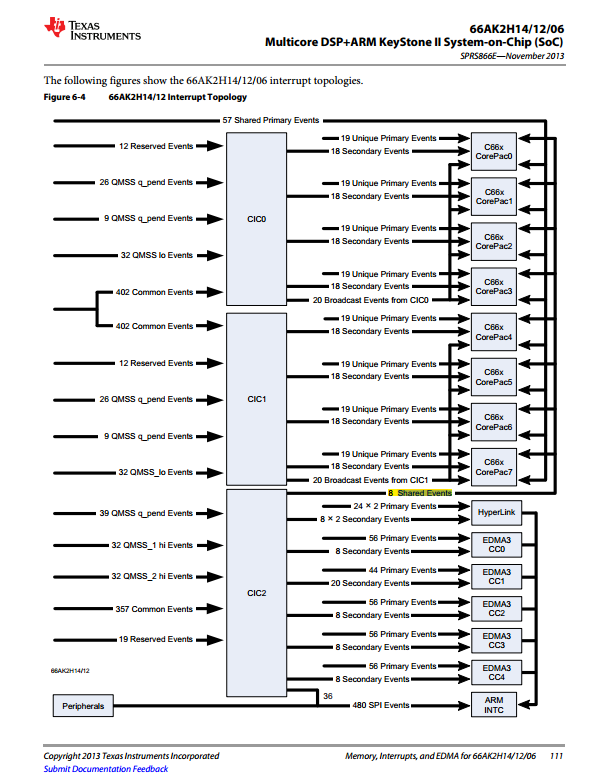

The following Figure 6-4 show the 66AK2H14/12 interrupt topologies.CIC2 has 103 event outputs which provides 8 Shared Events to each of the C66x CorePacs, 0 through 7.

I can't fand these on Table 6-22 (the mapping of system events),and host interrupt ID.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.