HI,

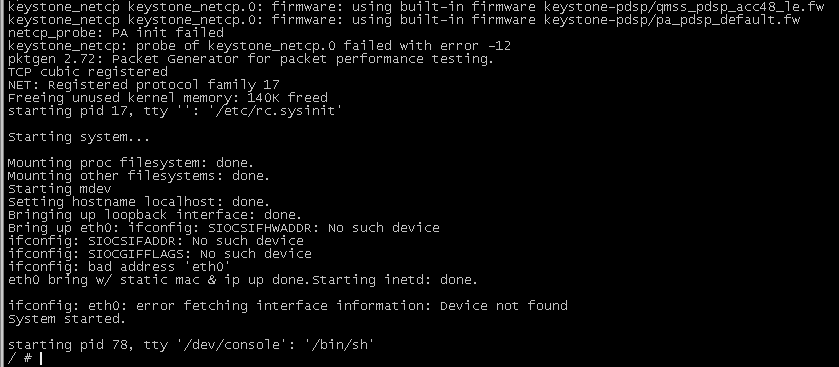

I am an developer of embedded Linux driver , I'm in the development of Linux drivers about 6678 platform, some problems encountered in the development of the network driver, I put the sgmii1 directly connected to the network switch chip BCM5396 port, I am using Ti drive of the original development board ,but the network does not work, requests for advice,thank you。