Using the UART in the C5505ezdsp REV C, I figured that the UART is not connected to the USB and that the output of the UART TX and RX are in the expansion connectors (as seen in the figure bellow). So I went ahead and soldered the pin 40 and 38 and then connected it to a max 232 chip which is outputed through DB9 connector. And from the DB9 female connector I used a serial to USB cable to transmit the information to the computer. Using the UART example provided, I tried to output what is expected on the terminal but nothing was functioning as expected. My question is I don't know whether I am setting up properly so that I could output the UART? Or maybe I am not using the proper code?

Thanks in advance for your help.

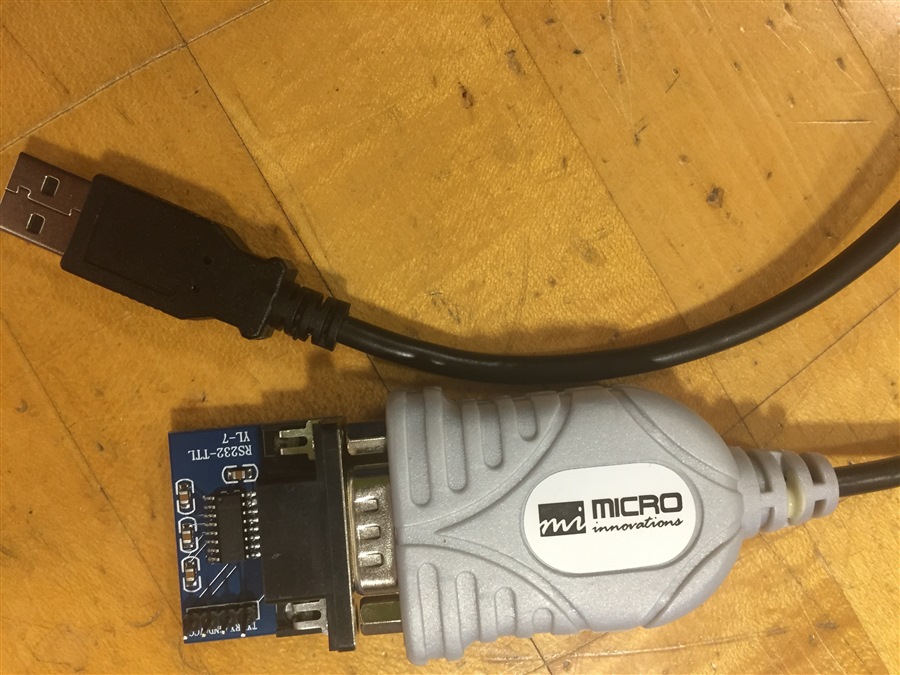

Figure 1: max 232 and the serial to usb cable

Figure 2: The c5505ezdsp connector

Code:

#include <stdio.h>

#include "csl_uart.h"

#include "csl_uartAux.h"

#include "csl_intc.h"

#include "csl_general.h"

#include "csl_error.h"

#define CSL_TEST_FAILED (1U)

#define CSL_TEST_PASSED (0)

#define CSL_UART_BUF_LEN (4U)

/* Global constants */

/* String length to be received and transmitted */

#define WR_STR_LEN 80

#define RD_STR_LEN 10

#define CSL_PLL_DIV_000 (0)

#define CSL_PLL_DIV_001 (1u)

#define CSL_PLL_DIV_002 (2u)

#define CSL_PLL_DIV_003 (3u)

#define CSL_PLL_DIV_004 (4u)

#define CSL_PLL_DIV_005 (5u)

#define CSL_PLL_DIV_006 (6u)

#define CSL_PLL_DIV_007 (7u)

#define CSL_PLL_CLOCKIN (32768u)

/* Global data definition */

/* UART setup structure */

CSL_UartSetup mySetup =

{

/* Input clock freq in MHz */

100000000,

/* Baud rate */

2400,

/* Word length of 8 */

CSL_UART_WORD8,

/* To generate 1 stop bit */

0,

/* Disable the parity */

CSL_UART_DISABLE_PARITY,

/* Enable trigger 14 fifo */

CSL_UART_FIFO_DMA1_DISABLE_TRIG14,

/* Loop Back enable */

CSL_UART_NO_LOOPBACK,

/* No auto flow control*/

CSL_UART_NO_AFE ,

/* No RTS */

CSL_UART_NO_RTS ,

};

/* CSL UART data structures */

CSL_UartObj uartObj;

CSL_UartHandle hUart;

/* CSL UART data buffers */

Uint16 uartIntcWriteBuff[CSL_UART_BUF_LEN ];

Uint16 uartIntcReadBuff[CSL_UART_BUF_LEN ];

char buffer1[30];

char buffer2[10];

char buffer3[30];

Uint16 gcount = 16;

Uint16 mutex = 0;

char *ptr = buffer1;

Uint16 setbit;

volatile Bool endOfTest = FALSE;

/* Interrupt vector start address */

extern void VECSTART(void);

/**

* \brief Function to calculate the system clock

*

* \param none

*

* \return System clock value in Hz

*/

Uint32 getSysClk(void);

/**

* \brief Interrupt Service Routine to handle UART Line Status Interrupt

*

* \param none

*

* \return none

*/

void uart_lsiIsr(void)

{

Uint16 reg;

reg=hUart->uartRegs->LSR;

reg= reg;

}

/**

* \brief Interrupt Service Routine to handle UART Character Timeout Interrupt

*

* \param none

*

* \return none

*/

void uart_ctoIsr(void)

{

UART_read( hUart,buffer2,0,0);

ptr = buffer2;

gcount = 1;

UART_eventEnable(hUart,CSL_UART_XMITOR_REG_EMPTY_INTERRUPT);

}

/**

* \brief Interrupt Service Routine to handle UART Transmit Interrupt

*

* \param none

*

* \return none

*/

void uart_txIsr(void)

{

if(gcount == 1)

{

UART_write(hUart, buffer3, 2, 0);

UART_write(hUart, ptr, gcount, 0);

if(*ptr == '$')

{

endOfTest = TRUE;

}

gcount = 13;

}

if(endOfTest == FALSE)

{

UART_write( hUart,buffer1,gcount,0);

}

UART_eventDisable(hUart, CSL_UART_XMITOR_REG_EMPTY_INTERRUPT);

}

/**

* \brief Interrupt Service Routine to handle UART Receive Interrupt

*

* \param none

*

* \return none

*/

void uart_rxIsr(void)

{

UART_read( hUart,buffer2,12,0);

gcount = 1;

UART_eventEnable(hUart,CSL_UART_XMITOR_REG_EMPTY_INTERRUPT);

}

/**

* \brief Interrupt Dispatcher to identify interrupt source

*

* This function identify the type of UART interrupt generated and

* calls concerned ISR to handle the interrupt

*

* \param none

*

* \return none

*/

interrupt void UART_intrDispatch(void)

{

Uint16 eventId = 0;

IRQ_disable(UART_EVENT);

/* Get the event Id which caused interrupt */

eventId = UART_getEventId(hUart);

if (((void (*)(void))(hUart->UART_isrDispatchTable[eventId])))

{

((void (*)(void))(hUart->UART_isrDispatchTable[eventId]))();

}

IRQ_enable(UART_EVENT);

return;

}

/**

* \brief UART interrupt Test function

*

* This function verifies the UART operation in interrupt mode.

* This function runs in an infinite loop to read the characters

* from HyperTerminal and echo the characters back to HyperTerminal.

*

* \param none

*

* \return Test result(Only Failure Case)

*/

CSL_Status uart_IntcSample(void)

{

CSL_UartIsrAddr isrAddr;

CSL_Status status;

Uint32 sysClk;

sysClk = getSysClk();

mySetup.clkInput = sysClk;

/* Loop counter and error flag */

status = UART_init(&uartObj,CSL_UART_INST_0,UART_INTERRUPT);

if(CSL_SOK != status)

{

printf("UART_init failed error code %d\n",status);

return(status);

}

else

{

printf("UART_init Successful\n");

}

/* Handle created */

hUart = (CSL_UartHandle)(&uartObj);

/* Configure UART registers using setup structure */

status = UART_setup(hUart,&mySetup);

if(CSL_SOK != status)

{

printf("UART_setup failed error code %d\n",status);

return(status);

}

else

{

printf("UART_setup Successful\n");

}

// /* Send the details of the test to HyperTerminal */

status = UART_fputs(hUart,"\r\n\nUART INTERRUPT TEST!",0);

if(CSL_SOK != status)

{

printf("UART_fputs failed error code %d\n",status);

return(status);

}

status = UART_fputs(hUart,"\r\nTEST READS A CHARACTER FROM HYPERTERMINAL CONTINUOUSLY",0);

if(CSL_SOK != status)

{

printf("UART_fputs failed error code %d\n",status);

return(status);

}

status = UART_fputs(hUart,"\r\nENTER '$' TO END THE TEST\r\n",0);

if(CSL_SOK != status)

{

printf("UART_fputs failed error code %d\n",status);

return(status);

}

/* Configure and Register the UART interrupts */

isrAddr.rbiAddr = uart_rxIsr;

isrAddr.tbeiAddr = uart_txIsr;

isrAddr.ctoi = uart_ctoIsr;

isrAddr.lsiAddr = uart_lsiIsr;

/* Disable interrupt */

IRQ_globalDisable();

/* Clear any pending interrupts */

IRQ_clearAll();

/* Disable all the interrupts */

IRQ_disableAll();

IRQ_setVecs((Uint32)(&VECSTART));

/* Configuring Interrupt */

IRQ_plug (UART_EVENT, &UART_intrDispatch);

/* Enabling Interrupt */

IRQ_enable(UART_EVENT);

IRQ_globalEnable();

/* Set the UART callback function */

status = UART_setCallback(hUart,&isrAddr);

if(status != CSL_SOK)

{

printf("UART_setCallback Failed\n");

return(status);

}

/* Enable the UART Events */

status = UART_eventEnable(hUart, CSL_UART_XMITOR_REG_EMPTY_INTERRUPT);

if(status != CSL_SOK)

{

printf("UART_eventEnable Failed\n");

return(status);

}

status = UART_eventEnable(hUart, CSL_UART_RECVOR_REG_DATA_INTERRUPT);

if(status != CSL_SOK)

{

printf("UART_eventEnable Failed\n");

return(status);

}

status = UART_eventEnable(hUart, CSL_UART_RECVOR_LINE_STATUS_INTERRUPT);

if(status != CSL_SOK)

{

printf("UART_eventEnable Failed\n");

return(status);

}

/* Tests runs until users enters Symbol '$' on the HyperTerminal */

while(endOfTest == FALSE)

{

printf("Enter something");

}

// UART_fgets(hUart,Char * pBuf, Uint16 bufSize, Uint32 timeout);

// UART_fputs(hUart,"\r\nTEST READS A CHARACTER FROM HYPERTERMINAL CONTINUOUSLY",0);

/* Disable interrupt */

IRQ_globalDisable();

/* Clear any pending interrupts */

IRQ_clearAll();

/* Disable all the interrupts */

IRQ_disableAll();

}

/**

* \brief Configures Dma

*

* \param chanNum - Dma channel number

*

* \return Dma handle

*/

/////INSTRUMENTATION FOR BATCH TESTING -- Part 1 --

///// Define PaSs_StAtE variable for catching errors as program executes.

///// Define PaSs flag for holding final pass/fail result at program completion.

volatile Int16 PaSs_StAtE = 0x0001; // Init to 1. Reset to 0 at any monitored execution error.

volatile Int16 PaSs = 0x0000; // Init to 0. Updated later with PaSs_StAtE when and if

///// program flow reaches expected exit point(s).

/////

void main()

{

CSL_Status status;

status = uart_IntcSample();

if(status != CSL_SOK)

{

printf("\nCSL UART INTERRUPT MODE TEST FAILED!!\n");

/////INSTRUMENTATION FOR BATCH TESTING -- Part 2 --

///// Reseting PaSs_StAtE to 0 if error detected here.

PaSs_StAtE = 0x0000; // Was intialized to 1 at declaration.

/////

}

else

{

printf("\nCSL UART INTERRUPT MODE TEST COMPLETED!!\n");

}

/////INSTRUMENTATION FOR BATCH TESTING -- Part 3 --

///// At program exit, copy "PaSs_StAtE" into "PaSs".

PaSs = PaSs_StAtE; //If flow gets here, override PaSs' initial 0 with

///// // pass/fail value determined during program execution.

///// Note: Program should next exit to C$$EXIT and halt, where DSS, under

///// control of a host PC script, will read and record the PaSs' value.

/////

}

/**

* \brief Function to calculate the clock at which system is running

*

* \param none

*

* \return System clock value in Hz

*/

#if (defined(CHIP_C5505_C5515) || defined(CHIP_C5504_C5514))

Uint32 getSysClk(void)

{

Bool pllRDBypass;

Bool pllOutDiv;

Uint32 sysClk;

Uint16 pllVP;

Uint16 pllVS;

Uint16 pllRD;

Uint16 pllVO;

pllVP = CSL_FEXT(CSL_SYSCTRL_REGS->CGCR1, SYS_CGCR1_VP);

pllVS = CSL_FEXT(CSL_SYSCTRL_REGS->CGCR1, SYS_CGCR1_VS);

pllRD = CSL_FEXT(CSL_SYSCTRL_REGS->CGICR, SYS_CGICR_RDRATIO);

pllVO = CSL_FEXT(CSL_SYSCTRL_REGS->CGOCR, SYS_CGOCR_OD);

pllRDBypass = CSL_FEXT(CSL_SYSCTRL_REGS->CGICR, SYS_CGICR_RDBYPASS);

pllOutDiv = CSL_FEXT(CSL_SYSCTRL_REGS->CGOCR, SYS_CGOCR_OUTDIVEN);

sysClk = CSL_PLL_CLOCKIN;

if (0 == pllRDBypass)

{

sysClk = sysClk/(pllRD + 4);

}

sysClk = (sysClk * ((pllVP << 2) + pllVS + 4));

if (1 == pllOutDiv)

{

sysClk = sysClk/(pllVO + 1);

}

/* Return the value of system clock in KHz */

return(sysClk);

}

#else

Uint32 getSysClk(void)

{

Bool pllRDBypass;

Bool pllOutDiv;

Bool pllOutDiv2;

Uint32 sysClk;

Uint16 pllVP;

Uint16 pllVS;

Uint16 pllRD;

Uint16 pllVO;

Uint16 pllDivider;

Uint32 pllMultiplier;

pllVP = CSL_FEXT(CSL_SYSCTRL_REGS->CGCR1, SYS_CGCR1_MH);

pllVS = CSL_FEXT(CSL_SYSCTRL_REGS->CGICR, SYS_CGICR_ML);

pllRD = CSL_FEXT(CSL_SYSCTRL_REGS->CGICR, SYS_CGICR_RDRATIO);

pllVO = CSL_FEXT(CSL_SYSCTRL_REGS->CGOCR, SYS_CGOCR_ODRATIO);

pllRDBypass = CSL_FEXT(CSL_SYSCTRL_REGS->CGICR, SYS_CGICR_RDBYPASS);

pllOutDiv = CSL_FEXT(CSL_SYSCTRL_REGS->CGOCR, SYS_CGOCR_OUTDIVEN);

pllOutDiv2 = CSL_FEXT(CSL_SYSCTRL_REGS->CGOCR, SYS_CGOCR_OUTDIV2BYPASS);

pllDivider = ((pllOutDiv2) | (pllOutDiv << 1) | (pllRDBypass << 2));

pllMultiplier = ((Uint32)CSL_PLL_CLOCKIN * ((pllVP << 2) + pllVS + 4));

switch(pllDivider)

{

case CSL_PLL_DIV_000:

case CSL_PLL_DIV_001:

sysClk = pllMultiplier / (pllRD + 4);

break;

case CSL_PLL_DIV_002:

sysClk = pllMultiplier / ((pllRD + 4) * (pllVO + 4) * 2);

break;

case CSL_PLL_DIV_003:

sysClk = pllMultiplier / ((pllRD + 4) * 2);

break;

case CSL_PLL_DIV_004:

case CSL_PLL_DIV_005:

sysClk = pllMultiplier;

break;

case CSL_PLL_DIV_006:

sysClk = pllMultiplier / ((pllVO + 4) * 2);

break;

case CSL_PLL_DIV_007:

sysClk = pllMultiplier / 2;

break;

}

/* Return the value of system clock in KHz */

return(sysClk);

}

#endif