I have interfaced a FPGA with DSK6416 by using a ASRAM interfacing technique. When transferring data from EDMA configured as

I have interfaced a FPGA with DSK6416 by using a ASRAM interfacing technique. When transferring data from EDMA configured as

EDMA_Config myConfig1 = {

0x21200001, // Frame Synchronized 1D-to-1D Transfer

0xA0000000, // Source address (Asynchronous Memory - FPGA)

0x00020004, // No of frame for transfer(16 bit)-1 || No of element per frame

0x80000000, // Destination address (On board SDRAM)

0x00000000, // Offset after frame

0x00040000 // rld

};

EDMA_config(hEdma1,&myConfig1); // Configure EDMA with parameter of myConfig1

EDMA_enableChannel(hEdma1); // Generating interrupt EER

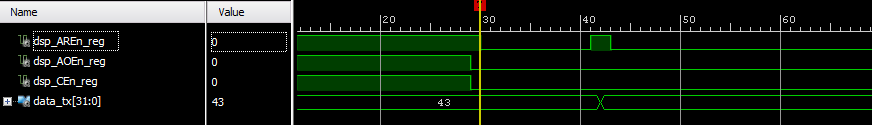

The read enable signal goes high only for first time then it become inactive? What could be the issue?