TI Team,

My team has built a custom board using the AM5K2E04 SoC. We are trying to get u-boot working using the k2e_evm_config as a start, but we have a few different peripherals than the TI K2E EVM board. Right now, we get to a prompt, but most things aren't fully functional. Ethernet initializes, but doesn't connect. SPI identifies the N25Q128A, but cannot read it. NAND throws errors when trying to write to it.

We want to know how to fix these issues and get Ethernet, NAND, SPI, and our VxWorks 7 OS working correctly.

Our board status:

- XDS200 fails to reset the processor (using the 66AK2E05 gel file) so we abandoned using it.

- It doesn't have a BMC.

- SPI flash and NAND are empty.

- UART works.

- Ethernet connections have green LEDs.

- We can change the boot mode using the FPGA to edit the DEVSTAT register.

Our u-boot build process so far:

- Downloaded latest keystone-linux u-boot, with latest cross-compiler.

- make k2e_evm_config

- Edited the ddr3 registers config, ddr3 spd logic, and ks2_evm.h variables.

- Built u-boot.bin

- Padded u-boot.bin to make u-boot.uart (so the start was at 0x0c001000)

- Booted board in UART mode

- Used Teraterm to XMODEM over the u-boot.uart BLOB.

- U-boot gets to a prompt.

HW changes between our custom AM5K2E04 board and the K2E EVM:

- ETH: 2 Ethernet ports start at PHY address 8, instead of 0. Using M88E1145 (Marvel) device, instead of M88E1111.

- SPI: Micron (St Micro) N25Q128A device

- NAND: Micron MT29F16G08ADBC device (2 GB)

- DDR3: 8 banks of 512MB (total 4 GB) starts at 0x08 0000 0000.

Error Symptoms:

- VxWorks 7 crashes almost immediately (at an MCR p15 assembly call to enable MMU)

- Ethernet LEDs are on, but pings and tftp timeout.

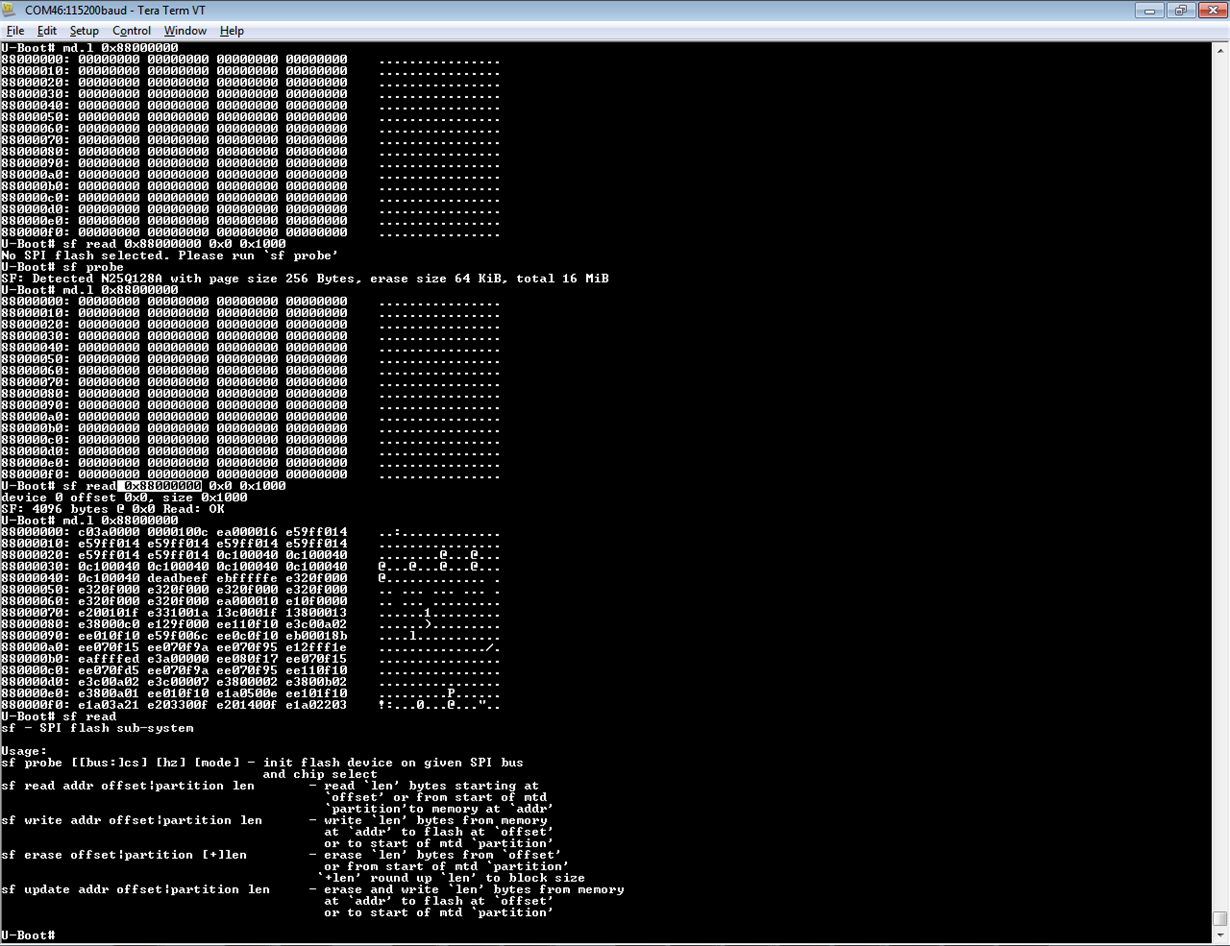

- 'sf probe' returns correct part name, but 'sf read' doesn't return anything.

- NAND writes throw an error: 'MTD Erase failure: -5'

Every register we check is set up as expected. Looking for help.

- Samuel Smith, Northrop Grumman Team