Hi,

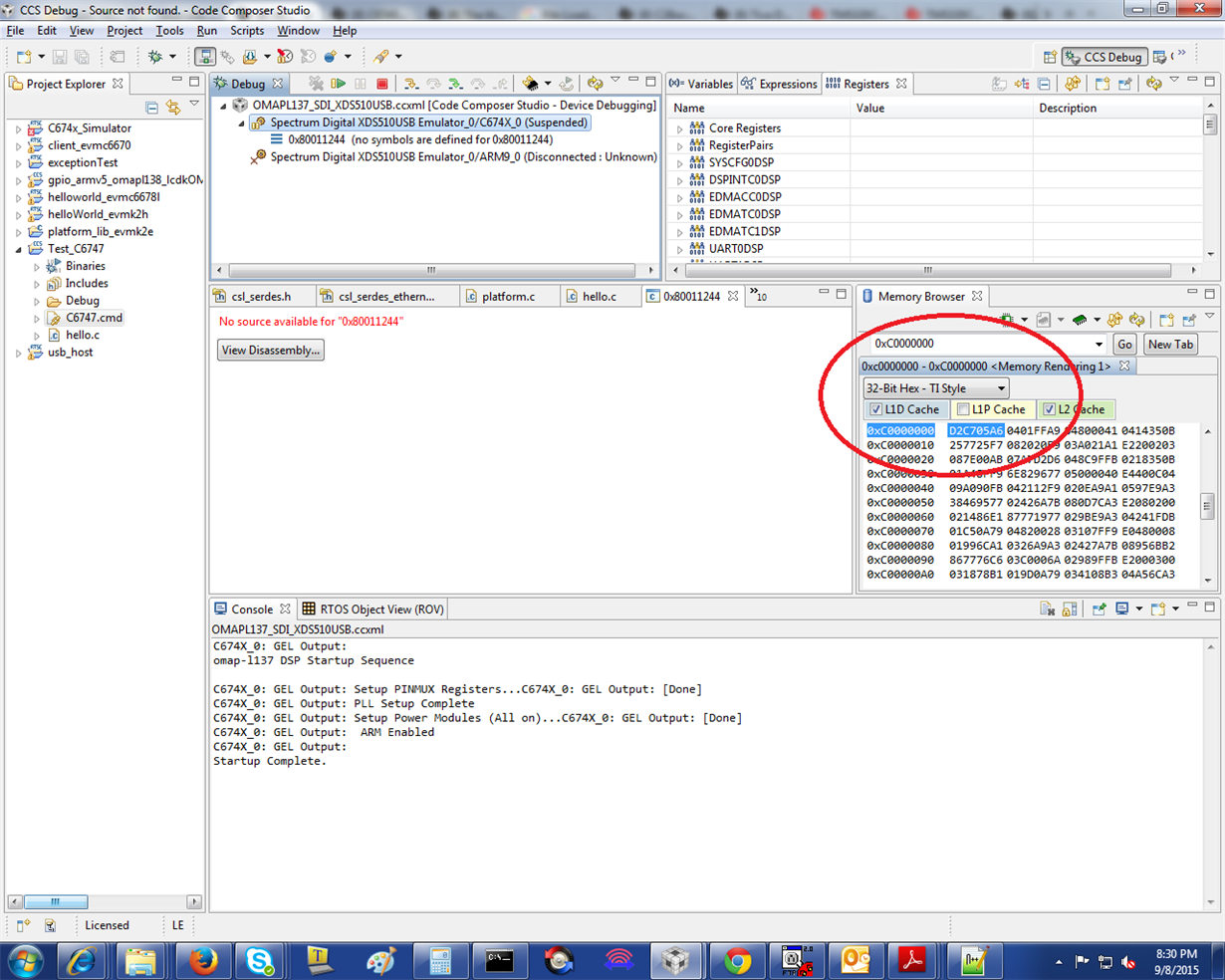

I am trying to configure the DDR2/mDDR memory controller and I am currently following the steps to initialise the module in section 13.2.13.1 of the technical reference. I am also using the example in the cslr for guidance. I realise that the registers provided in the cslr do not match the ones in my watch list as shown in the picture below.

While the register description matches, the names of the registers provided do not have the same name as the one in my watch list, furthermore it seems that some of the registers listed in the technical reference manual are missing. Is there a known solution to solve this? Thank you.

Regards,

Jerome Lieow