Hi TI Team,

I would like to run lcd driver in 1bpp (MONOCHROME) mode on LCD 320x240 (PG320240WRF) with 4-bit output mode.

The driver is da8xx-fb with modifications for support DeviceTree and MONO01 for fb (fb_probe function):

if (da8xx_fb_info->var.bits_per_pixel == 1)

da8xx_fb_info->fix.visual = FB_VISUAL_MONO01;

PWR pin is managed as gpio and enabled at the driver start.

I have fb settings: continuous memory for fb (32B + 9600B) as palette memory and data.

The palette configuration is as follow (fb_setcolreg function):

switch (info->fix.visual)

{

case FB_VISUAL_MONO01:

switch (info->var.bits_per_pixel) {

case 1:

if (regno > 15)

return -EINVAL;

if (regno == 0)

pal = 0x0000;

else if (regno == 1)

pal = 0x000f;

else

pal = 0;

After configuration I have regs values:

----- regs -----

0x00 : 0x4f201000

0x04 : 0x0000ba01

0x28 : 0x00080003

0x2c : 0x00000270

0x30 : 0x000000ef

0x34 : 0x00000000

0x40 : 0x00000541

0x44 : 0x8f240020

0x48 : 0x8f24259c

0x4c : 0x8f240020

0x50 : 0x8f24259c

0x58 : 0x00000042

0x5c : 0x00000000

0x60 : 0x00000324

0x64 : 0x00000324

0x68 : 0x00000000

0x6c : 0x00000005

0x70 : 0x00000000

I can see palette values:

----- Memory dump: palette -----

[0xd0873000] 00000f00000000000000000000000000 00000000000000000000000000000000

and data (first bytes) for loaded raw file with "0xff 0xff 0xff 0xff" at the begin, rest of the fb is 0x00:

----- Memory dump: dma -----

[0xd0873020] FFFFFFFF000000000000000000000000 00000000000000000000000000000000

[0xd0873040] 00000000000000000000000000000000 00000000000000000000000000000000

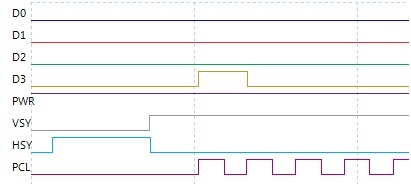

Unfortunatelly, on oscilloscope I see only PCLK, VSYNC, HSYNC without any data for first 32 bits

and in magnification

What shoud I change for see proper view on LCD? What is wrong in configuration?

Thanks in advance,

Rafal