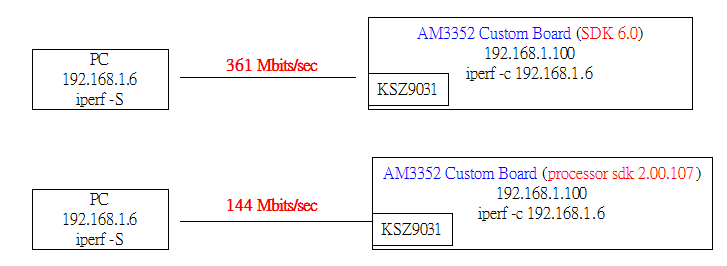

We use the same AM3352 Custom Board,and Run iperf as following

Why is there such a difference???

in SDK6 board-am335xevm.c

#define MMD_ACCESS_CTRL 0xd

#define MMD_ACCESS_REG_DATA 0xe

#define MMD_ACCESS_REG_MODE 0x0000

#define MMD_ACCESS_DATANOPOST_MODE 0x4000

#define MMD_ACCESS_DATAPOST_MODE 0x8000

#define MMD_ACCESS_DATAPOSTWRTONLY_MODE 0xc000

#define KSZ9031_PHY_CLK_PAD_SKEW_REG 0x08

#define KSZ9031_RGMII_CLK_DLY 0x2d6

#define KSZ9031_PHY_RXD_PAD_SKEW_REG 0x05

#define KSZ9031_RGMII_RXD_DLY 0x0000

static int wise_dly_phy_fixup(struct phy_device *phydev)

{

int temp;

/// CLK

phy_write(phydev, MMD_ACCESS_CTRL,MMD_ACCESS_REG_MODE|0x02);

phy_write(phydev, MMD_ACCESS_REG_DATA, KSZ9031_PHY_CLK_PAD_SKEW_REG);

phy_write(phydev, MMD_ACCESS_CTRL,MMD_ACCESS_DATANOPOST_MODE|0x02);

temp = phy_read(phydev, MMD_ACCESS_REG_DATA);

pr_info("phy read clk = 0x%x\n",temp);

phy_write(phydev, MMD_ACCESS_REG_DATA, (temp&0xFC00) | KSZ9031_RGMII_CLK_DLY);

temp = phy_read(phydev, MMD_ACCESS_REG_DATA);

pr_info("phy read clk = 0x%x\n",temp);

/// RXData

phy_write(phydev, MMD_ACCESS_CTRL,MMD_ACCESS_REG_MODE|0x02);

phy_write(phydev, MMD_ACCESS_REG_DATA, KSZ9031_PHY_RXD_PAD_SKEW_REG);

phy_write(phydev, MMD_ACCESS_CTRL,MMD_ACCESS_DATANOPOST_MODE|0x02);

temp = phy_read(phydev, MMD_ACCESS_REG_DATA);

pr_info("phy read rxd = 0x%x\n",temp);

phy_write(phydev, MMD_ACCESS_REG_DATA, KSZ9031_RGMII_RXD_DLY);

temp = phy_read(phydev, MMD_ACCESS_REG_DATA);

pr_info("phy read rxd = 0x%x\n",temp);

return 0;

}

in Processor SDK2.00 107 DTS file

&cpsw_emac0 {

phy_id = <&davinci_mdio>, <0>;

phy-mode = "rgmii-txid";

dual_emac_res_vlan = <1>;

/* clock skew correction, maximum possible on KSZ9031 is

2^5 - 1 * 0,06ns = 1860ps, micrel datasheet M9999-081712-0.11 p.58*/

rxc-skew-ps = <726>;

txc-skew-ps = <726>;

/* align rx signals to zero, leave tx to default */

rxd0-skew-ps = <0>;

rxd1-skew-ps = <0>;

rxd2-skew-ps = <0>;

rxd3-skew-ps = <0>;

};