hi all,

i have configured emif in synch mode and i am transferring data from fpga fifo to c6455 dsp thru emif.

i have used edma to read that data.

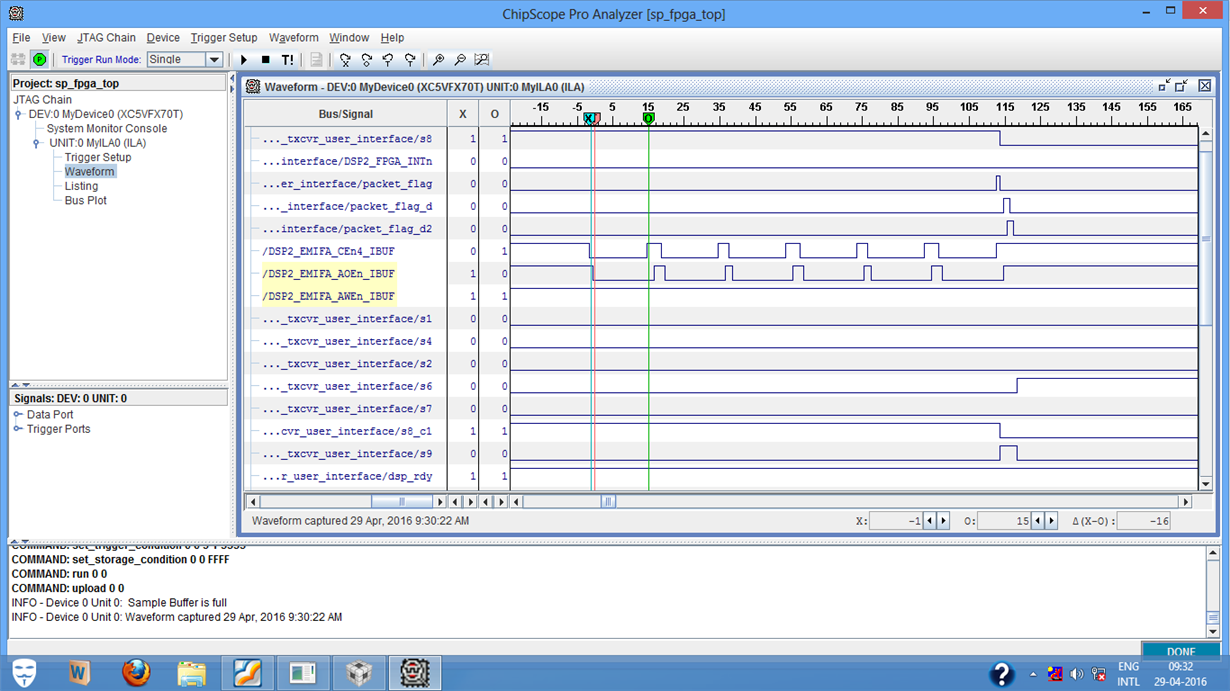

i have given in edma function to read 768 bytes of data(which is 96 no of 64 bit words). what i observed is that there is an idle time(ce high) of 4 emif clock cycles for every 16 emif reads. how can i reduce it to 0? pls find the attached figure for reference.

one more observation is, between 2 edma reads there is an idle time(ce high) of 400 emif clock cycles.how can i reduce it to as low as possible?

in my code between successive edma reads there is some code which has an addition and receiving interrupt. The reason behind the ce low for huge time ..is it beacuse of this intermitent logic or the edma function is taking this much time for initiating next read or do i have to change any register value?

pls find the attached figure for refernce.

the ce cnfg register value is EMIFA_CE4CFG = 0x8000010B;

thanks in advance

vaishnavi.

this is my code which does the edma reads :

-------------------------------------------------------------------------------------------------

while(1){

rb = 0;

cnt= cnt + 1;

gpioInternalLoopbackDemo3();

while(rb < *range_bin){

gpioInternalLoopbackDemo();

rb = rb + 1;

if(rb == 1)

{

dst_addr_d = (Uint32)0xe0002000;

edma_write(0xc0000000,dst_addr_d,768);

}

else if( rb > 1 && rb < *range_bin)

{

dst_addr_d = dst_addr_d + (Uint32)0x300;

edma_write(0xc0000000,dst_addr_d,768);

}

else if(rb == *range_bin)

{

dst_addr_d = dst_addr_d + (Uint32)0x300;

edma_write(0xc0000000,dst_addr_d,768);

}

else

{

}

}

}

----------------------------------------------------------------------------------------------------------------

this is the edma_write function

void edma_write (Uint32 srcBuff1,Uint32 dstBuff1,int count)

{

CSL_Edma3Handle hModule;

CSL_Edma3HwSetup hwSetup;

CSL_Edma3Obj edmaObj;

CSL_Edma3ParamHandle hParamBasic;

CSL_Edma3ParamHandle hParamBasic2;

CSL_Edma3ChannelObj chObj;

CSL_Edma3ChannelObj chObj1;

CSL_Edma3ChannelObj chObj2;

CSL_Edma3CmdIntr regionIntr;

CSL_Edma3CmdDrae regionAccess;

CSL_Edma3ChannelHandle hChannel;

CSL_Edma3ChannelHandle hChannel2;

CSL_Edma3ParamSetup myParamSetup;

CSL_Edma3ParamSetup myParamSetup2;

CSL_Edma3Context context;

CSL_Edma3ChannelAttr chAttr;

CSL_Edma3ChannelAttr chAttr2;

CSL_Status status;

CSL_Edma3HwDmaChannelSetup dmahwSetup;

CSL_Edma3ChannelErr chErrClear;

volatile Uint32 loopIndex;

// printf ("Running Edma Example\n");

/* Module Initialization */

status = CSL_edma3Init(&context);

// if (status != CSL_SOK) {

// printf ("Edma module initialization failed\n");

// return;

// }

/* Module level open */

hModule = CSL_edma3Open(&edmaObj,CSL_EDMA3,NULL,&status);

// if ( (hModule == NULL) || (status != CSL_SOK)) {

// printf ("Edma module open failed\n");

// return;

// }

// CSL_Edma3HwDmaChannelSetup dmahwSetup[3] = CSL_EDMA3_DMACHANNELSETUP_DEFAULT;

/* Module setup */

dmahwSetup.paramNum = 0;

dmahwSetup.que = CSL_EDMA3_QUE_0;

hwSetup.dmaChaSetup = &dmahwSetup;

hwSetup.qdmaChaSetup = NULL;

status = CSL_edma3HwSetup(hModule,&hwSetup);

// if (status != CSL_SOK) {

/// printf ("Hardware setup failed\n");

// CSL_edma3Close (hModule);

// return;

// }

/* DRAE enable(Bits 0-15) for the shadow region 5 */

regionAccess.region = CSL_EDMA3_REGION_5 ;

regionAccess.drae = 0xFFFF ;

regionAccess.draeh = 0x0 ;

status = CSL_edma3HwControl(hModule,CSL_EDMA3_CMD_DMAREGION_ENABLE, \

®ionAccess);

// if (status != CSL_SOK) {

// printf ("Edma region enable command failed\n");

// return;

// }

/* Channel 0 open in context of shadow region 5 */

chAttr.regionNum = CSL_EDMA3_REGION_5;

chAttr.chaNum = CSL_EDMA3_CHA_DSP_EVT;

hChannel = CSL_edma3ChannelOpen(&chObj, CSL_EDMA3, &chAttr, &status);

// if ((hChannel == NULL) || (status != CSL_SOK)) {

// printf ("Edma channel open failed\n");

// return;

// }

/* Obtain a handle to parameter set 0 */

hParamBasic = CSL_edma3GetParamHandle(hChannel,0,&status);

// if (hParamBasic == NULL) {

// printf ("Edma get param handle for param entry 0 failed\n");

// return;

// }

/* Setup the param set */

myParamSetup.option = CSL_EDMA3_OPT_MAKE( CSL_EDMA3_ITCCH_DIS, \

CSL_EDMA3_TCCH_EN, \

CSL_EDMA3_ITCINT_DIS, \

CSL_EDMA3_TCINT_EN,\

4,

CSL_EDMA3_TCC_NORMAL,\

CSL_EDMA3_FIFOWIDTH_NONE, \

CSL_EDMA3_STATIC_DIS, \

CSL_EDMA3_SYNC_A, \

CSL_EDMA3_ADDRMODE_INCR, \

CSL_EDMA3_ADDRMODE_INCR

);

myParamSetup.srcAddr = (Uint32)srcBuff1;

myParamSetup.aCntbCnt = CSL_EDMA3_CNT_MAKE(count,1);

myParamSetup.dstAddr = (Uint32)dstBuff1;

myParamSetup.srcDstBidx = CSL_EDMA3_BIDX_MAKE(0,0);

myParamSetup.linkBcntrld = CSL_EDMA3_LINKBCNTRLD_MAKE(CSL_EDMA3_LINK_NULL,1);

myParamSetup.srcDstCidx = CSL_EDMA3_CIDX_MAKE(0,0);

myParamSetup.cCnt = 1;

status = CSL_edma3ParamSetup(hParamBasic, &myParamSetup);

// if (status != CSL_SOK) {

// printf("Edma parameter entry setup is failed1\n");

// return;

// }

//

//

/* Channel 4 open in context of shadow region 5 */

// chAttr2.regionNum = CSL_EDMA3_REGION_5;

// chAttr2.chaNum = CSL_EDMA3_CHA_4;

// hChannel2 = CSL_edma3ChannelOpen(&chObj2, CSL_EDMA3, &chAttr2, &status);

// if ((hChannel2 == NULL) || (status != CSL_SOK)) {

// printf ("Edma channel open failed\n");

// return;

// }

/* Obtain a handle to parameter set 8 */

// hParamBasic2 = CSL_edma3GetParamHandle(hChannel2,4,&status);

/* Setup the param set */

// myParamSetup2.option = CSL_EDMA3_OPT_MAKE(CSL_EDMA3_ITCCH_DIS, \

CSL_EDMA3_TCCH_EN, \

CSL_EDMA3_ITCINT_DIS, \

CSL_EDMA3_TCINT_EN, \

1, \

CSL_EDMA3_TCC_NORMAL, \

CSL_EDMA3_FIFOWIDTH_NONE, \

TRUE,CSL_EDMA3_SYNC_AB, \

CSL_EDMA3_ADDRMODE_INCR, \

CSL_EDMA3_ADDRMODE_INCR

// );

// myParamSetup2.srcAddr = (Uint32)srcBuff1;

// myParamSetup2.aCntbCnt = CSL_EDMA3_CNT_MAKE(count,2);

// myParamSetup2.dstAddr = (Uint32)dstBuff1+50;

// myParamSetup2.srcDstBidx = CSL_EDMA3_BIDX_MAKE(count,count);

// myParamSetup2.linkBcntrld = CSL_EDMA3_LINKBCNTRLD_MAKE(CSL_EDMA3_LINK_NULL,0);

// myParamSetup2.srcDstCidx = CSL_EDMA3_CIDX_MAKE(0,1);

// myParamSetup2.cCnt = 1;

// status = CSL_edma3ParamSetup(hParamBasic2,&myParamSetup2);

// if (status != CSL_SOK) {

// printf("Edma parameter entry setup is failed\n");

// return;

// }

/* Enable channel 0 */

status = CSL_edma3HwChannelControl(hChannel,CSL_EDMA3_CMD_CHANNEL_ENABLE, NULL);

// if (status != CSL_SOK) {

// printf("Edma channel enable command for channel 0 is failed\n");

// return;

// }

/* Enable channel 4 */

// status = CSL_edma3HwChannelControl(hChannel2,CSL_EDMA3_CMD_CHANNEL_ENABLE, \

NULL);

// if (status != CSL_SOK) {

// printf("Edma channel enable command for channel 4 is failed\n");

// return;

// }

/* Trigger Channel 0 */

CSL_edma3HwChannelControl(hChannel,CSL_EDMA3_CMD_CHANNEL_SET,NULL);

regionIntr.region = CSL_EDMA3_REGION_5;

// do {

// /* Poll on interrupt bit 8 */

// CSL_edma3GetHwStatus(hModule,CSL_EDMA3_QUERY_INTRPEND,®ionIntr);

// } while (!(regionIntr.intr & 0x1));

//

//

// /* Clear interrupt bit 8 */

// status = CSL_edma3HwControl(hModule,CSL_EDMA3_CMD_INTRPEND_CLEAR, \

// ®ionIntr);

// if (status != CSL_SOK) {

// printf("Edma clear interrupt bit 0 command is failed\n");

// return;

// }

/* Disable the region 5 */

regionAccess.region = CSL_EDMA3_REGION_5 ;

regionAccess.drae = 0xFFFF ;

regionAccess.draeh = 0x0 ;

status = CSL_edma3HwControl(hModule,CSL_EDMA3_CMD_DMAREGION_ENABLE, \

®ionAccess);

/* clear the EDMA error registers */

chErrClear.missed = TRUE;

chErrClear.secEvt = TRUE;

CSL_edma3HwChannelControl (hChannel, CSL_EDMA3_CMD_CHANNEL_DISABLE, NULL);

CSL_edma3HwChannelControl (hChannel, CSL_EDMA3_CMD_CHANNEL_CLEARERR,

&chErrClear);

CSL_edma3HwChannelControl (hChannel, CSL_EDMA3_CMD_CHANNEL_CLEAR, NULL);

/* Close channel */

status = CSL_edma3ChannelClose(hChannel);

// if (status != CSL_SOK) {

// printf("Edma channel close failed\n");

// return;

// }

/* Close edma module */

status = CSL_edma3Close(hModule);

// if (status != CSL_SOK) {

// printf("Edma module close failed\n");

// return;

// }

// printf ("=============================================================\n");

return;

}

-----------------------------------------------------------------------------------------------------------------