Refer to SDK6.0

【problem description】

Step1、Two A8 am3352 boards, Send a set of data(0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa),from MasterA UART1 to SlaveB UART5

Step2、Operation Process: Board Power down ——————>Board Power Up——————>Send a set of data(0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa) from UART1 to UART5

Step3、Repeat above Operation . In this process,we found the receive data is not correct .

1)Step2 ,there is a certain probability , Occurrence of the following conditions:

First group

UART1 Send [0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa]

UART5 Recv [0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa, 0x0]

Second group

UART1 Send [0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa]

UART5 Recv [0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa, 0x47]

Third group

UART1 Send [0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa]

UART5 Recv [0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa, 0x6d]

Fourth group

UART1 Send [0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa]

UART5 Recv [0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa, 0x70]

Fifth group

UART1 Send [0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa]

UART5 Recv [0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa, 0x2d]

Sixth group

UART1 Send [0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa]

UART5 Recv [0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa, 0xce]

Seventh group

UART1 Send [0x1, 0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa]

UART5 Recv [0x2, 0x3, 0x4, 0x5, 0x6, 0x7, 0x8, 0x9, 0xa, 0x7]

Problem phenomenon :The set of data is missed the first data,thus tha last data make up by random data.

【Doubts】

1、According to the catched waveform chart, Data and waveform consistency;

2、It only occur condition:power down and up

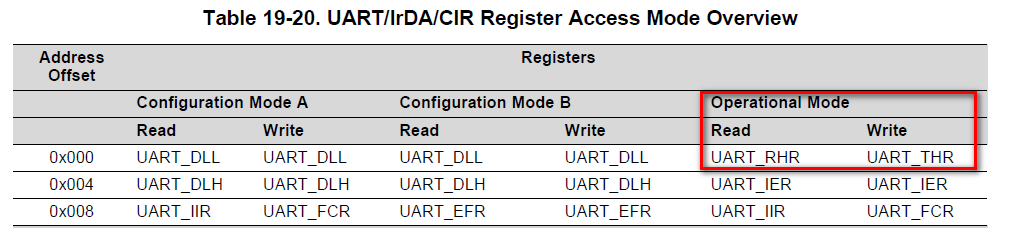

Therefore suspect :before am335x uart's Tx FiFo active,Did not do empty FIFO action ?

Waiting online~